Verifica diseños de procesadores RISC-V complejos

Lyra es un marco de trabajo que verifica diseños de procesadores RISC-V complejos. Resuelve el cuello de botella que supone simular con software lento y usar estímulos de prueba aleatorios de baja calidad. En lugar de depender de mutaciones ciegas, Lyra integra un modelo generativo especializado que entiende la arquitectura del conjunto de instrucciones. Este modelo, llamado LyraGen, produce secuencias de instrucciones semánticamente ricas y de alta calidad para explorar comportamientos complejos del hardware.

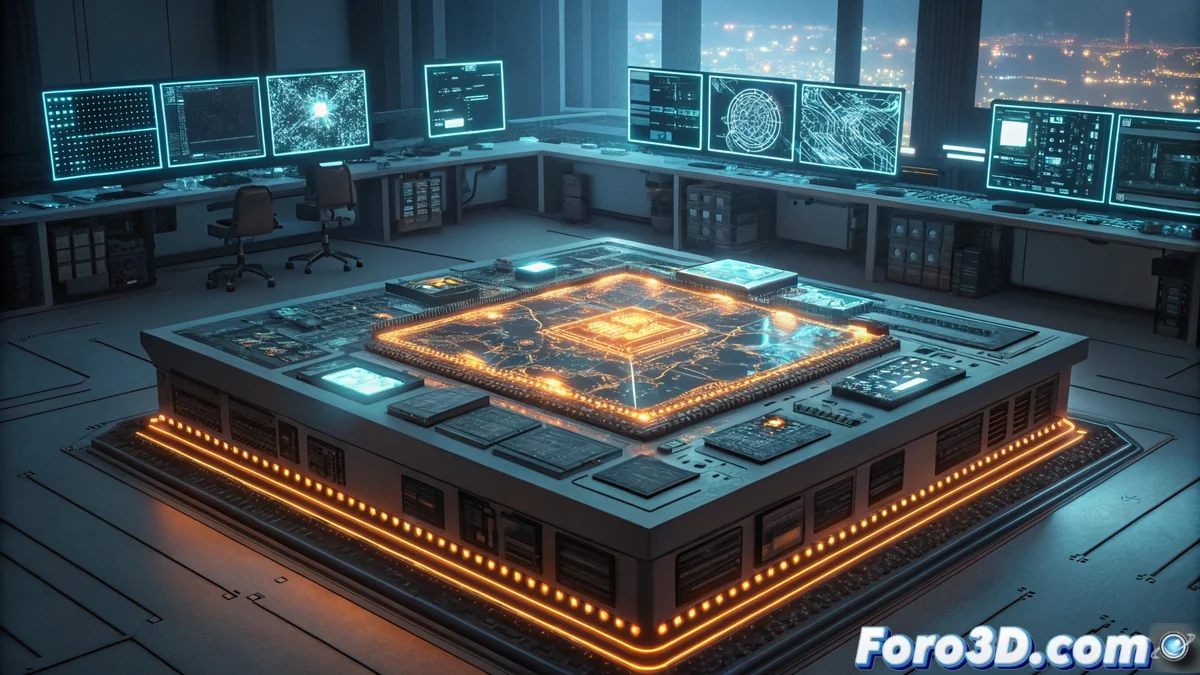

La arquitectura acelera la verificación en hardware

El sistema ejecuta la unidad bajo prueba y el modelo de referencia al mismo tiempo en un SoC con FPGA. Este enfoque permite comprobar las diferencias a alto rendimiento y recopilar la cobertura a nivel de hardware de forma masiva. Al combinar esta aceleración con los estímulos inteligentes de LyraGen, el marco supera las limitaciones de los verificadores de software tradicionales.

Los resultados empíricos muestran una ganancia significativa

Las pruebas experimentales indican que Lyra logra una cobertura hasta 1.27 veces mayor. Además, acelera el proceso de verificar de extremo a extremo entre 107 y 3343 veces en comparación con los verificadores de software más avanzados. El sistema también demuestra una dificultad de convergencia consistentemente menor, lo que reduce el costo total de verificar.

Claro, porque lo que siempre ha necesitado el diseño de chips es que una IA le explique pacientemente qué instrucciones son interesantes para ejecutar, en lugar de golpear el teclado aleatoriamente hasta que algo falle.

|Agradecer cuando alguien te ayuda es de ser agradecido|

Citar

Citar