Intel Foundry детализирует свой специализированный аппаратный обеспечения для ИИ и HPC

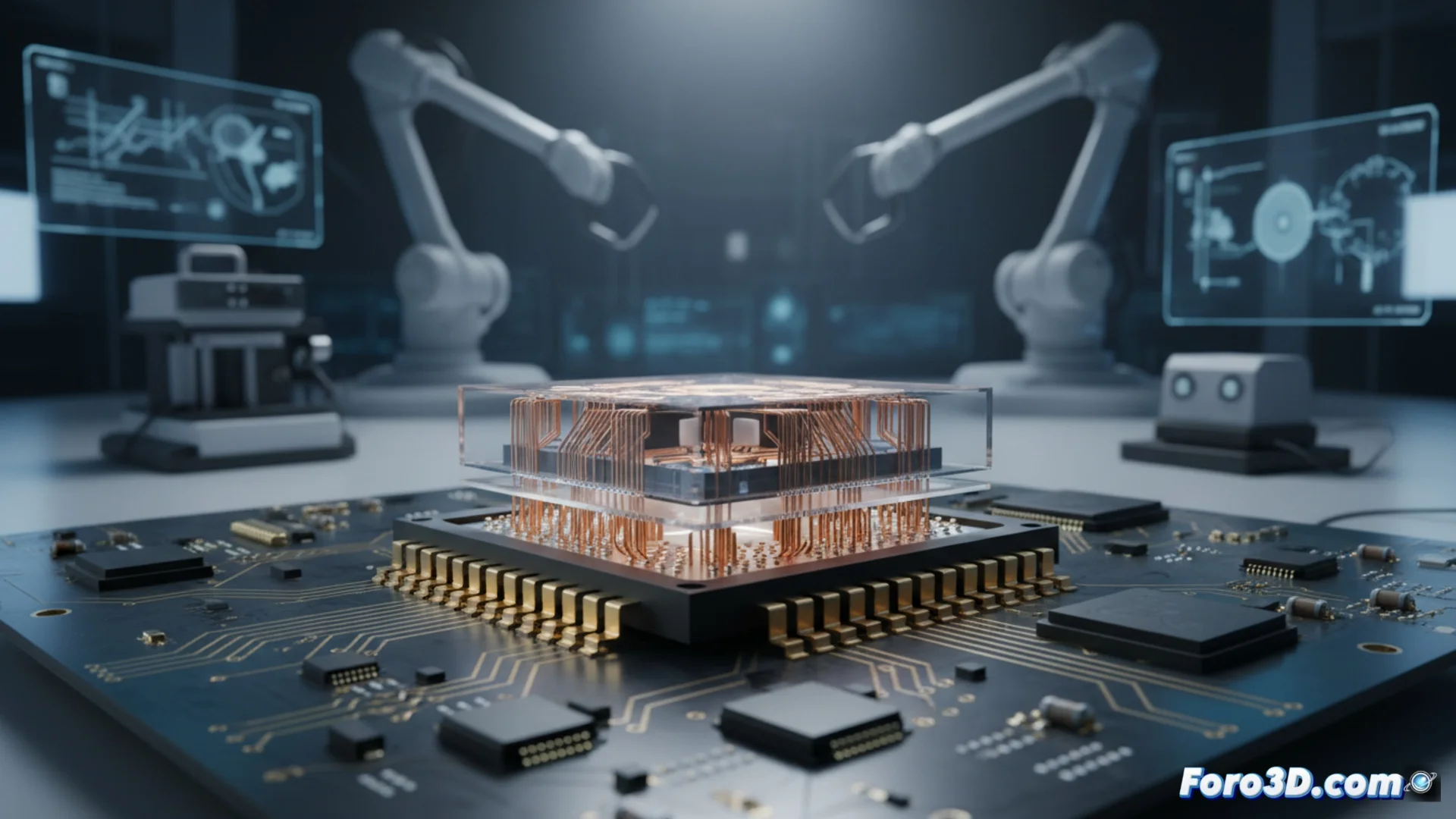

Подразделение по производству Intel раскрыло технический отчет, в котором объясняет, как разрабатывает и производит физические компоненты, предназначенные для выполнения задач искусственного интеллекта и высокопроизводительных вычислений. Документ сопровождается презентацией чипа валидации, который демонстрирует текущие возможности компании по интеграции нескольких элементов в одном устройстве. 🧠

Варианты производства и передовой упаковки

Опубликованные материалы уточняют альтернативы производства, которые Intel Foundry предлагает своим клиентам. Здесь приведены данные о передовых технологических узлах, таких как Intel 18A, и методах объединения нескольких чиплетов или фрагментов кремния. Цель этих решений — создание более мощных и эффективных систем путем объединения вычислительных ядер, быстрой памяти и элементов соединения в одном пакете.

Ключевые детали документа:- Описание самых передовых доступных технологических узлов.

- Технологии для эффективной интеграции нескольких чиплетов.

- Фокус на создании полных и оптимизированных систем в одном пакете.

Тестовый чип — это первый crucial шаг для валидации технологий перед их массовым производством.

Валидация возможностей 3D-упаковки

Прототип для ИИ, который демонстрирует Intel, включает несколько фундаментальных инноваций. Он использует архитектуру PowerVia для управления распределением энергии и технологию Foveros Direct для соединения чипов в 3D с использованием медных соединений. Эта стратегия позволяет stacking компонентов, таких как процессоры и модули памяти, чтобы сократить расстояние, которое проходят данные, и таким образом оптимизировать как производительность, так и энергопотребление.

Технологии, реализованные в тестовом чипе:- Архитектура PowerVia для более эффективной подачи энергии.

- Foveros Direct для высокоплотных 3D-медных межсоединений.

- Возможность stacking компонентов и снижения задержек.

Шаг к коммерческому будущему

Хотя технический отчет обширен и детализирован, чип валидации представляет собой лишь начальную фазу этого пути. Еще предстоит путь, чтобы эти достижения воплотились в конечные продукты, которые выйдут на рынок и станут доступны пользователям. Документ подчеркивает приверженность Intel расширять границы специализированного аппаратного обеспечения для самых требовательных вычислительных задач. ⚙️