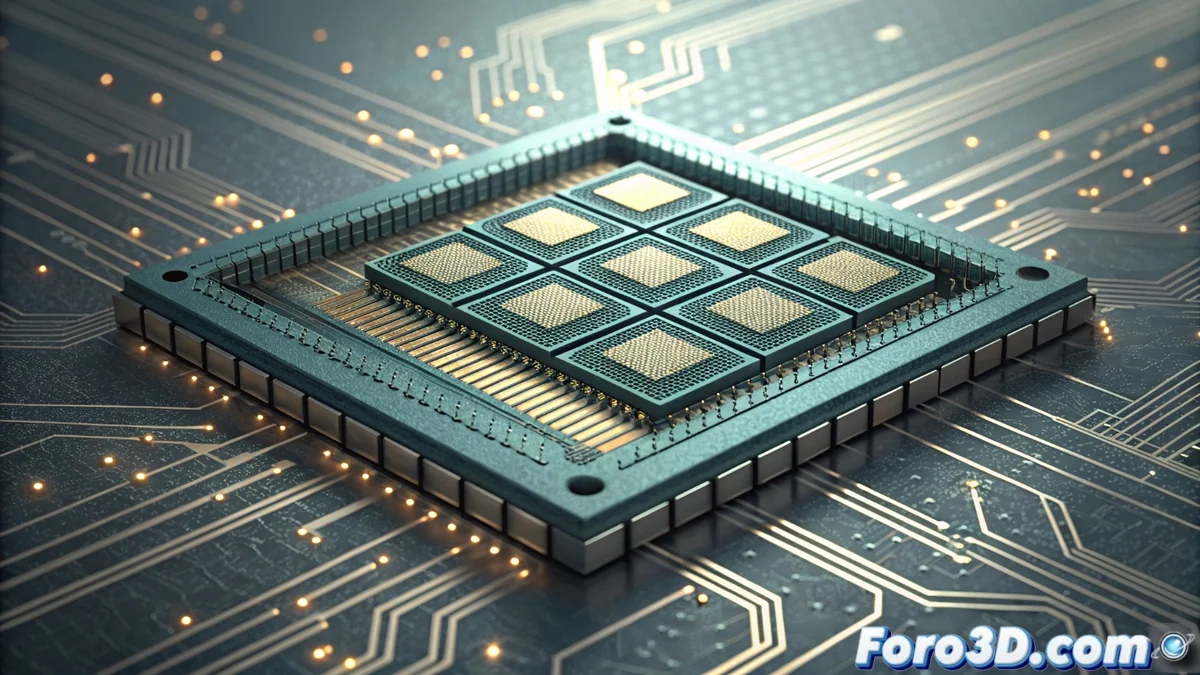

A arquitetura PIM: processamento em memória como revolução do hardware

O design de hardware está passando por uma transformação radical com o surgimento da arquitetura PIM (Processamento em Memória). Esse paradigma desafia décadas de convenção ao colocar a lógica de cálculo diretamente dentro dos módulos de memória, sejam DDR ou as avançadas pilhas HBM (High Bandwidth Memory). O princípio é executar operações onde os dados residem, eliminando a necessidade de mover informações massivas através do barramento do sistema para a CPU ou GPU. Essa mudança promete resolver o gargalo mais crítico da computação moderna. 🚀

Vantagens transformadoras e casos de uso

O impacto da PIM se manifesta em duas dimensões chave: desempenho bruto e eficiência energética. Ao reduzir drasticamente o movimento de dados, consome uma fração da energia, um avanço crucial para centros de dados e supercomputação. As aplicações que lidam com grandes conjuntos de dados são as principais beneficiárias. Aqui, a latência despenca e a largura de banda efetiva se multiplica.

Áreas de aplicação chave:- Aprendizado de máquina e IA: Acelera o treinamento de modelos e a inferência ao processar matrizes de dados diretamente na memória.

- Análise de bancos de dados: Acelera consultas complexas e operações de filtragem e classificação em grandes volumes de informação.

- Simulação científica e renderização: Otimiza tarefas que requerem acesso intensivo a buffers e geometrias complexas, comum em gráficos 3D e CFD.

A ironia final é que, após décadas otimizando CPUs para mover dados mais rápido, a solução parece ser não movê-los de forma alguma.

Obstáculos no caminho da adoção

Apesar de seu potencial, a implementação da PIM não está livre de desafios profundos. Requer uma reinvenção completa das hierarquias de memória e do software que as gerencia. Os desenvolvedores precisam de novos modelos de programação e ferramentas para aproveitar esse processamento descentralizado.

Principais desafios a superar:- Complexidade de design: Integrar lógica de computação em chips de memória densos apresenta problemas de fabricação, dissipação de calor e confiabilidade.

- Ecossistema de software: São necessários compiladores, bibliotecas e frameworks novos que abstraiam a complexidade do hardware para os programadores.

- Arquitetura do sistema: A coordenação entre a CPU, GPU e as múltiplas unidades PIM na memória requer novos designs de interconexão e coerência.

O futuro e as implementações atuais

A indústria já está avançando com protótipos e primeiras soluções, sinalizando um caminho irreversível. Empresas como Samsung com suas memórias HBM-PIM, e gigantes como AMD e Intel com arquiteturas que exploram conceitos afins, estão liderando essa hibridização entre memória e processamento. Essa virada conceitual, que provavelmente Von Neumann não antecipou, redefine os fundamentos da computação, priorizando a proximidade dos dados sobre a velocidade de seu transporte. O futuro do hardware será, sem dúvida, mais integrado e eficiente. 💡