ASML은 내년부터 고개구수(High-NA) EUV 리소그래피의 대량 도입을 향해 나아가고 있습니다. 이 기술은 1.4 nm 주변 노드에서 칩의 대량 생산에 필수적입니다. Intel, Samsung, SK hynix가 초기 고객으로 꼽히며, TSMC는 비용 문제로 대규모 채택을 연기하여 2027-2028년에 보편적인 사용을 예상하고 있습니다.

기술적 도약: 0.55 개구수와 한 번에 8 nm 패턴 ⚙️

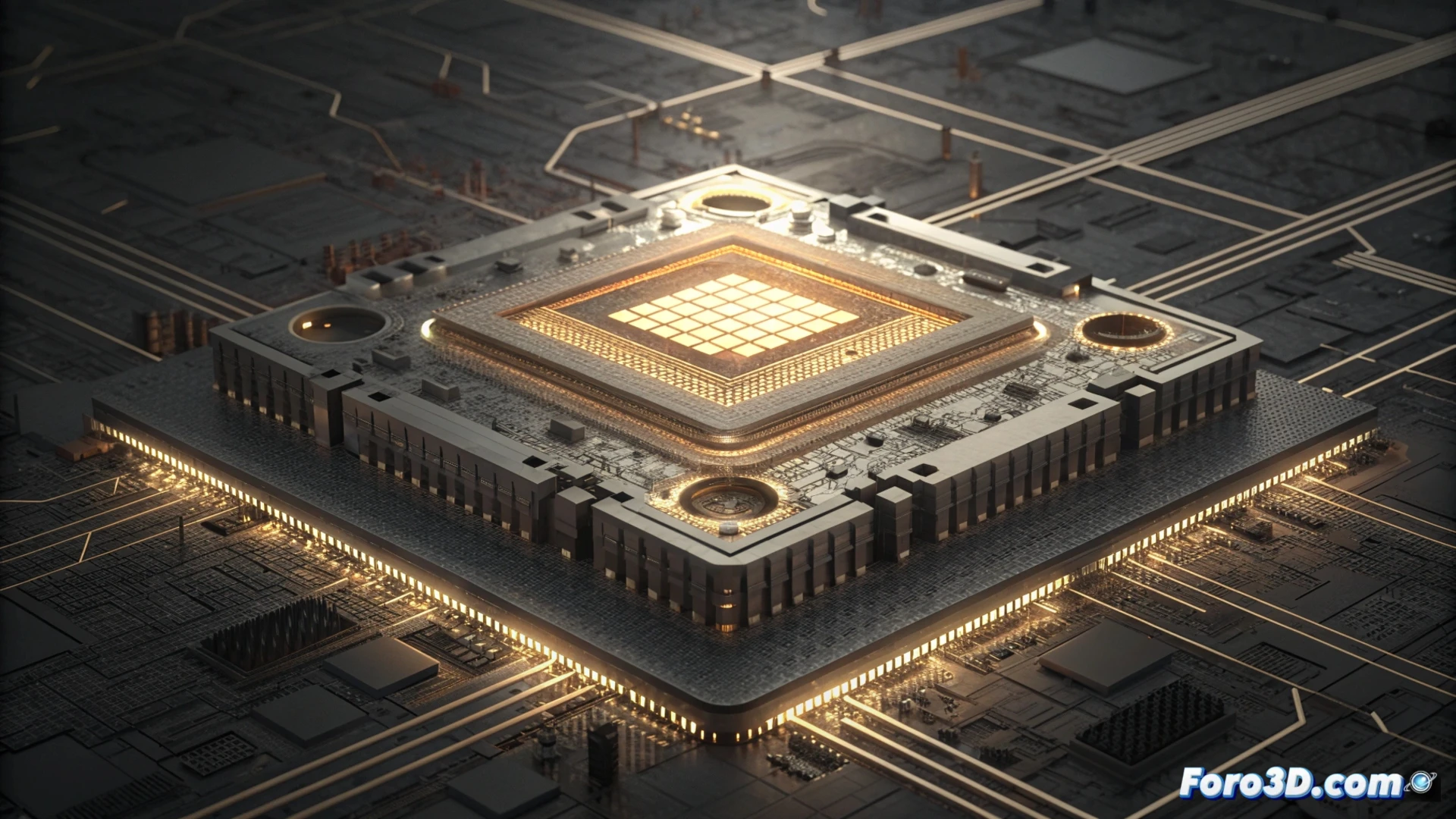

High-NA EUV 장비는 개구수를 현재 EUV 시스템의 0.33에서 0.55로 증가시킵니다. 이 변화는 단일 노출로 약 8 나노미터 패턴을 인쇄할 수 있게 하여, 고급 로직 및 메모리 노드의 제조 흐름을 단순화합니다. 더 미세한 특징을 해상하는 능력은 2 nm 이후 프로세스에 핵심입니다.

당신은 이미 3억 달러 스캐너를 예약하셨나요? 💸

반도체 거대 기업들이 주문을 계획하는 동안, 우리 나머지는 이 공학의 경이로움에 대한 가격을 되새길 수 있습니다. 각 시스템의 비용은 수억 달러에 달하며, 이는 마드리드에서 아파트를 사는 것처럼 보이는 지출을 사소하게 만듭니다. 1.4 nm 클럽에 가입하려면 좋은 의지와 실리콘 웨이퍼 몇 장 이상이 필요할 것 같습니다.