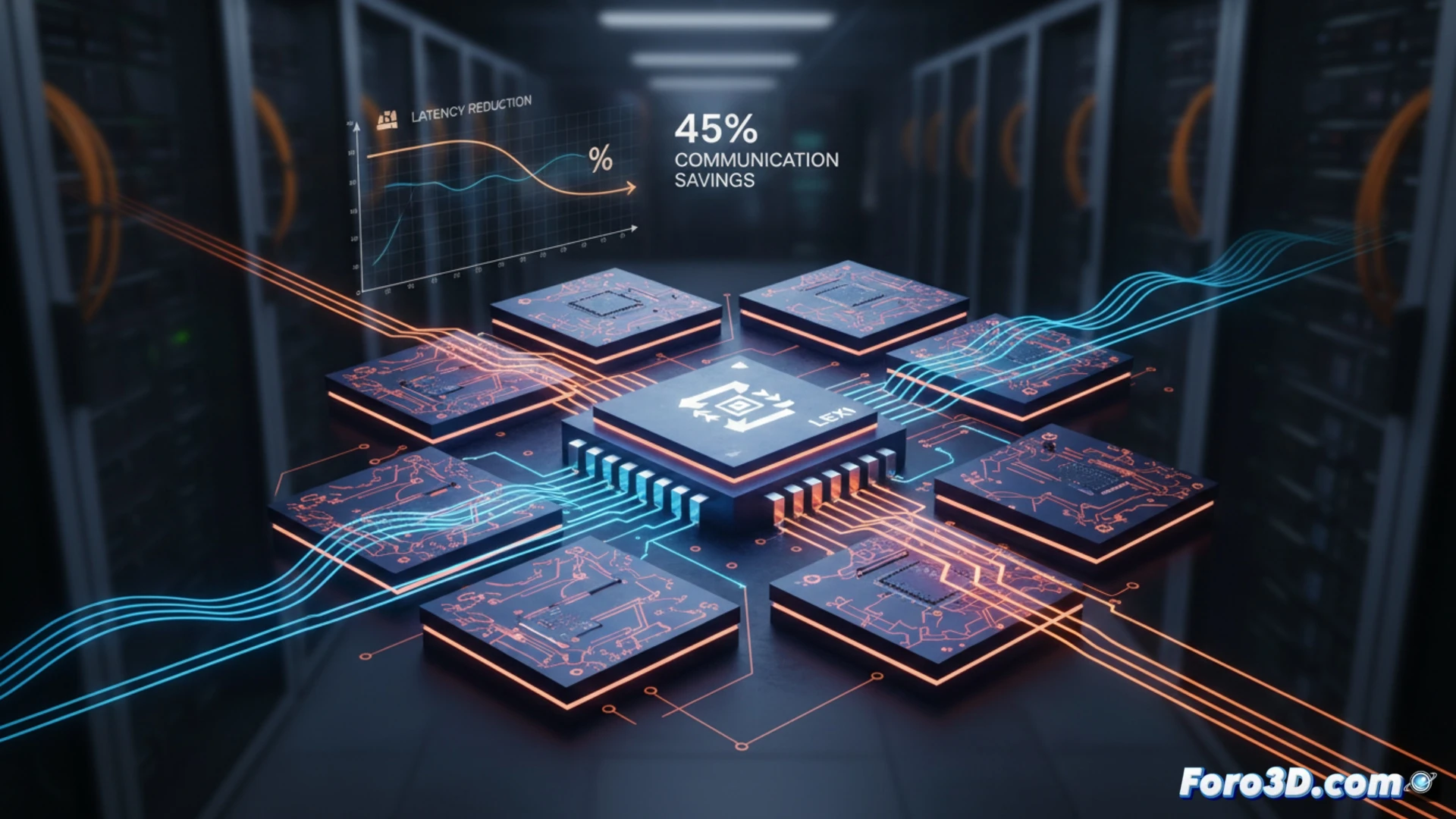

大規模言語モデル(LLM)の推論は、チップレット間のデータ移動のボトルネックによって制限されています。これらのモデルが主にBF16形式を使用しているため、分析により、指数部のフローが非常に低いエントロピー(3ビット未満)を持ち、高度に圧縮可能であることが明らかになりました。私たちはLEXIを提示します。これは、Huffmanベースの損失なし圧縮スキームで、チップ内ネットワーク(NoC)上で直接指数部を圧縮します。アクティベーション、キャッシュ、ウェイトを圧縮することで、LEXIはチップレットホモジニアスアーキテクチャにおいて、通信を33-45%、推論の総遅延を30-35%削減し、エリアとエネルギーのコストは最小限です。

LEXIコーデックのNoCにおけるアーキテクチャと実装 🧠

LEXIはチップ内ネットワークのルーターに直接統合されます。小さなコーデックが入出力ポートに配置され、BF16データの指数部をオンフライで圧縮・展開します。鍵は効率的なハードウェア実装にあります:マルチラインのルックアップテーブル(LUT)ベースのデコーダーを使用し、リンクの最大帯域幅を維持し、圧縮による遅延を回避します。ウェイトはメモリに圧縮状態で保存され、テンソルコアでの計算直前に展開されます。22nm GF技術で製造されたこのシステムのオーバーヘッドは、エリアとエネルギー消費でわずか0.09%であり、システム性能の大幅な向上に対する限界的なコストです。

AI向け半導体3D設計の未来への影響 🚀

LEXIは単なる圧縮技術を超え、AIのためのソフトウェアとハードウェアの共同設計におけるパラダイムシフトを表します。データリンクレベルで数値形式に固有の冗長性を攻撃することで、よりスケーラブルで効率的なチップレットアーキテクチャを可能にします。このアプローチは、現在の最大の制約の一つであるインターコネクト帯域幅の飽和を緩和します。3Dマイクロファブリケーションのニッチ分野において、LEXIは明確な前例を設定します:イノベーションは単にトランジスタやチップレットを積み重ねることではなく、それらの間で移動する各ビットをインテリジェントに最適化することにあり、LLM推論の新たな性能水準を解き放ちます。

指数部圧縮技術LEXIは、チップレット間のデータ転送をどのように最適化してLLM推論の遅延を削減するのでしょうか?

(PD: 200mmウェハをシミュレートするのはピザを作るようなもの:みんなが一片欲しがる)