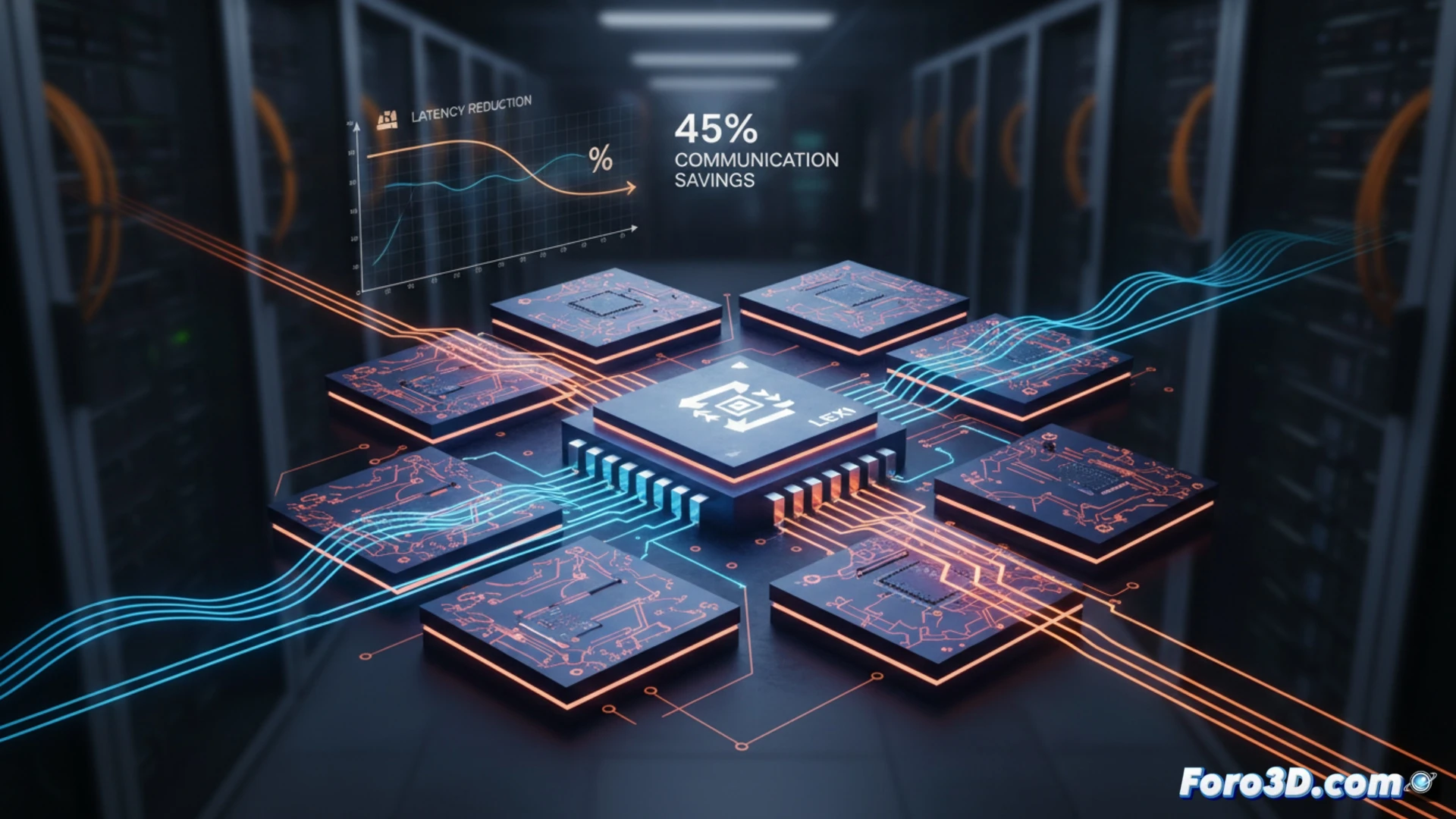

La inferencia en modelos de lenguaje grandes (LLM) se ve lastrada por el cuello de botella en el movimiento de datos entre chiplets. Dado que estos modelos usan predominantemente el formato BF16, un análisis revela que los flujos de exponentes poseen una entropía muy baja, inferior a 3 bits, lo que los hace altamente compresibles. Presentamos LEXI, un esquema de compresión sin pérdidas para exponentes basado en Huffman, que actúa directamente en la red en chip (NoC). Al comprimir activaciones, cachés y pesos, LEXI reduce la comunicación y la latencia total de inferencia entre un 33-45% y un 30-35%, respectivamente, en arquitecturas homogéneas de chiplets, con un coste de área y energía mínimo.

Arquitectura e Implementación del Codec LEXI en la NoC 🧠

LEXI se integra directamente en los routers de la red en chip. Pequeños códecs se sitúan en los puertos de entrada y salida, comprimiendo y descomprimiendo los exponentes de los datos BF16 sobre la marcha. La clave está en su implementación hardware eficiente: utiliza decodificadores basados en tablas de búsqueda (LUT) multilínea que mantienen el ancho de banda máximo del enlace, evitando que la compresión introduzca retardos. Los pesos se almacenan comprimidos en memoria y se descomprimen justo antes del cálculo en el núcleo tensor. Fabricado en tecnología GF de 22 nm, el overhead de este sistema es de solo un 0.09% en área y consumo energético, un coste marginal para una ganancia sustancial en rendimiento del sistema.

Impacto en el Futuro del Diseño 3D de Semiconductores para IA 🚀

LEXI trasciende una simple técnica de compresión; representa un cambio de paradigma en la co-diseño de software y hardware para IA. Al atacar la redundancia inherente en los formatos numéricos a nivel del enlace de datos, permite arquitecturas de chiplets más escalables y eficientes. Este enfoque mitúa uno de los mayores limitantes actuales: la saturación del ancho de banda de interconexión. Para el nicho de la microfabricación 3D, LEXI establece un precedente claro: la innovación no solo está en apilar más transistores o chiplets, sino en optimizar inteligentemente cada bit que viaja entre ellos, desbloqueando nuevas cotas de rendimiento en inferencia de LLMs.

¿Cómo puede la técnica de compresión de exponentes LEXI optimizar la transferencia de datos entre chiplets para reducir la latencia en la inferencia de LLMs?

(PD: simular una oblea de 200mm es como hacer una pizza: todo el mundo quiere un trozo)