Omni、DDR5に挑戦するオープン・メモリ・インターフェース

メモリ技術の風景の中で、新しい競合者が登場しています:オープン・メモリ・インターフェース(OMI)。この高速シリアルインターコネクトプロトコルは、JEDECの伝統的な標準である遍在するDDR5に対する直接的な代替として位置づけられています。その基本設計は、システムがデータにアクセスする方法を革命化することを目指しています。🚀

メモリのためのユニバーサル・ブリッジ

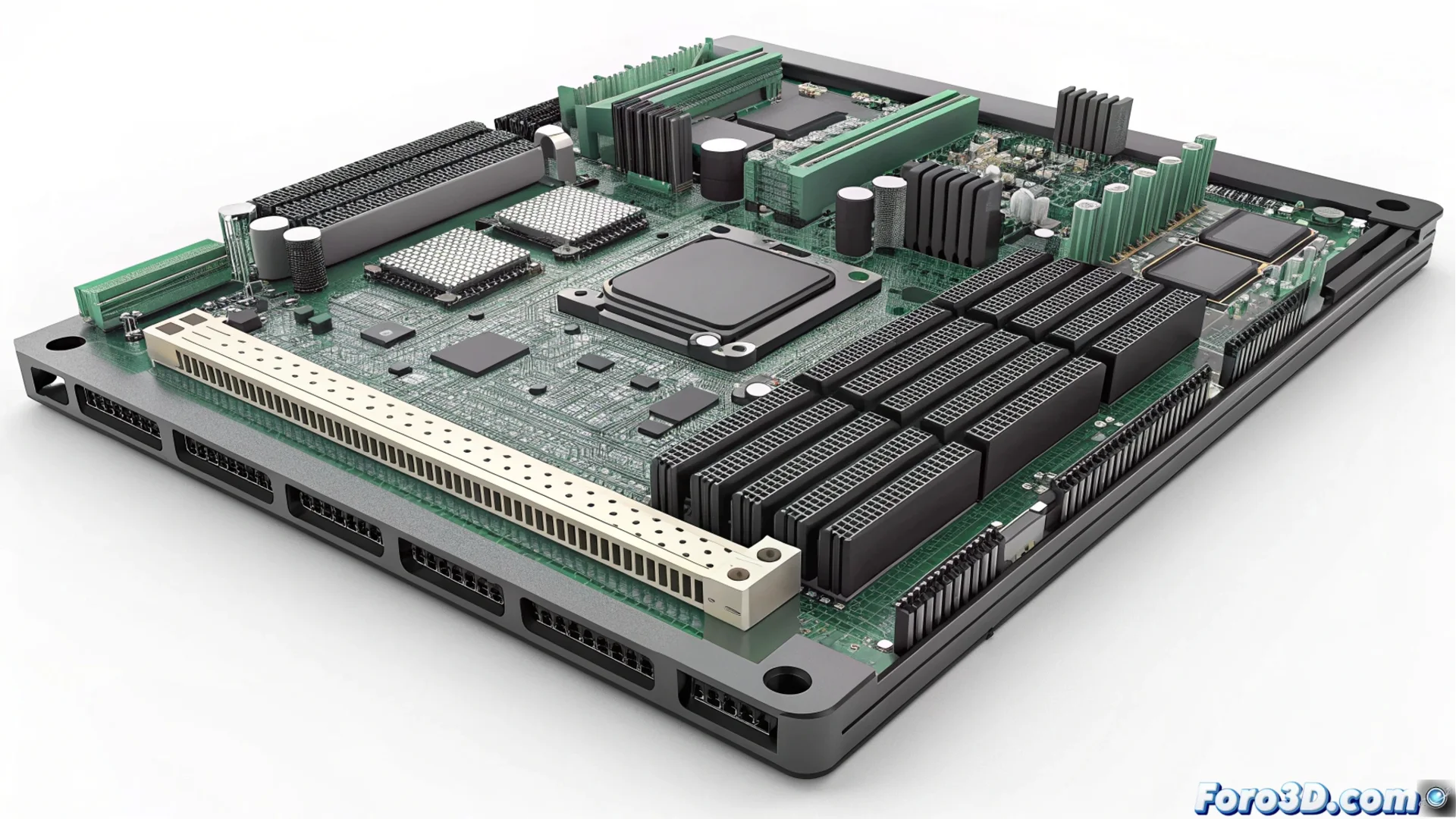

OMIの核心は、プロセッサチップ自体または非常に近いインターポーザに配置されるコントローラです。このコンポーネントは翻訳者および管理者として機能し、シリアルバスを介してメモリモジュールと通信します。鍵となる革新は、これらのモジュール、つまりOMI DIMMが、物理的に異なるメモリチップ技術を統合できる点にあります。コントローラは、DDR、GDDR、さらにはHBMの各チップが使用するネイティブプロトコルにプロセッサのリクエストを適応させます。

このアプローチの主な利点:- 設計の自由度:エンジニアはシステム全体で単一の物理メモリ標準に依存しません。

- レイテンシの低減:ダイレクトリンクアーキテクチャと効率的な管理により、アクセス遅延を最小限に抑えます。

- 有効帯域幅の増加:最も要求の厳しいニーズにデータフローを最適化します。

OMIはプロセッサとメモリの間の柔軟なブリッジとして機能し、ロジカルインターフェースを基底となる物理技術から分離します。

AIと高性能コンピューティングのための最適化

このプロトコルは、人工知能(AI)サーバーや高性能コンピューティング(HPC)などの専門環境でその存在意義を見出します。これらの分野では、メモリのニーズは多様で具体的です:一部のタスクは巨大な帯域幅を必要とし、他のものは巨大な容量を優先し、また他のものは最小限のレイテンシを要求します。OMIは、同じプラットフォーム内の各サブシステムに最適なメモリタイプを選択することを可能にします。

ヘテロジニアスシステムでの実用的アプリケーション:- GPUやAIアクセラレータのコアを加速するための高帯域幅HBMメモリモジュールを使用。

- 中央プロセッサ(CPU)のメイン・メモリプールのための大容量DDRメモリモジュールを使用。

- ワークロードのフェーズに応じて技術を混在させ、パフォーマンスと効率を最適化。

オープン標準の課題

メモリインターフェースの複雑なエコシステムを統一するオープン標準の提案は、理論的には非常に魅力的です。システム設計を簡素化し、低コスト化し、効率化することを約束します。しかし、技術産業の歴史は、善意がしばしば大手メーカーの商業的利益や既存投資と対立することを示しています。OMIの成功は、その採用と、JEDECの根強いインフラに対して具体的な説得力のある利点を証明できるかどうかにかかっています。道は開かれていますが、障害はありません。⚡