Omn, la interfaz de memoria abierta que desafía a ddr5

Omn, la interfaz de memoria abierta que desafía a ddr5

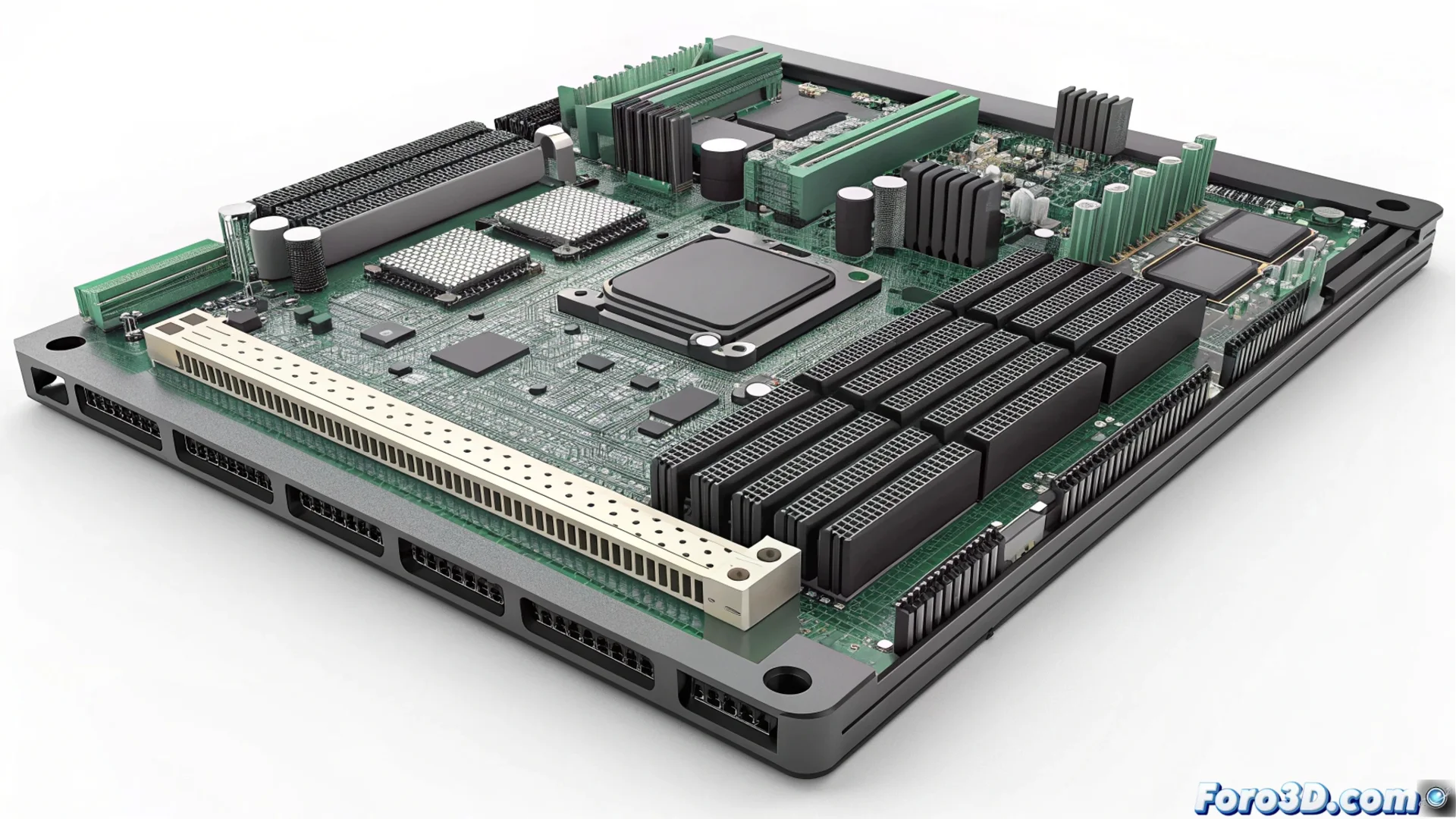

En el panorama de la tecnología de memoria, emerge un nuevo contendiente: la Interfaz de Memoria Abierta (OMI). Este protocolo de interconexión serie de alta velocidad se posiciona como una alternativa directa a los estándares tradicionales de JEDEC, como el omnipresente DDR5. Su diseño fundamental busca revolucionar cómo los sistemas acceden a los datos. 🚀

Un puente universal para la memoria

El núcleo de OMI es un controlador que se ubica en el propio chip del procesador o en un interpuesto muy cercano. Este componente actúa como un traductor y gestor, comunicándose con los módulos de memoria a través de un bus serie. La innovación clave reside en que estos módulos, llamados DIMM OMI, pueden integrar físicamente diferentes tecnologías de chips de memoria. El controlador se encarga de adaptar las peticiones del procesador al protocolo nativo que use cada chip, ya sea DDR, GDDR o incluso HBM.

Ventajas clave de este enfoque:- Libertad de diseño: Los ingenieros no dependen de un solo estándar de memoria física para todo el sistema.

- Reducir la latencia: La arquitectura de enlace directo y la gestión eficiente apuntan a minimizar los retrasos en el acceso.

- Aumentar el ancho de banda efectivo: Optimiza el flujo de datos para las demandas más exigentes.

OMI funciona como un puente flexible entre el procesador y la memoria, desacoplando la interfaz lógica de la tecnología física subyacente.

Optimizar para IA y computación de alto rendimiento

Este protocolo encuentra su razón de ser en entornos especializados como servidores para inteligencia artificial (IA) y computación de alto rendimiento (HPC). En estos campos, las necesidades de memoria son diversas y específicas: algunas tareas requieren un ancho de banda monumental, otras priorizan una capacidad enorme y otras exigen una latencia mínima. OMI permite elegir el tipo de memoria más idóneo para cada subsistema dentro de la misma plataforma.

Aplicaciones prácticas en un sistema heterogéneo:- Usar módulos con memoria HBM de alto ancho de banda para acelerar los núcleos de una GPU o un acelerador de IA.

- Emplear módulos con memoria DDR de gran capacidad para el pool de memoria principal del procesador central (CPU).

- Mezclar tecnologías según la fase de la carga de trabajo, optimizando así el rendimiento y la eficiencia.

El desafío de un estándar abierto

La propuesta de un estándar abierto que unifique el complejo ecosistema de interfaces de memoria es, en teoría, muy atractiva. Promete simplificar, abaratar y hacer más eficientes los diseños de sistemas. Sin embargo, la historia de la industria tecnológica muestra que las buenas intenciones a menudo se enfrentan a los intereses comerciales y las inversiones establecidas de los grandes fabricantes. El éxito de OMI dependerá de su adopción y de si logra demostrar ventajas tangibles y convincentes frente a la arraigada infraestructura de JEDEC. El camino está abierto, pero no exento de obstáculos. ⚡