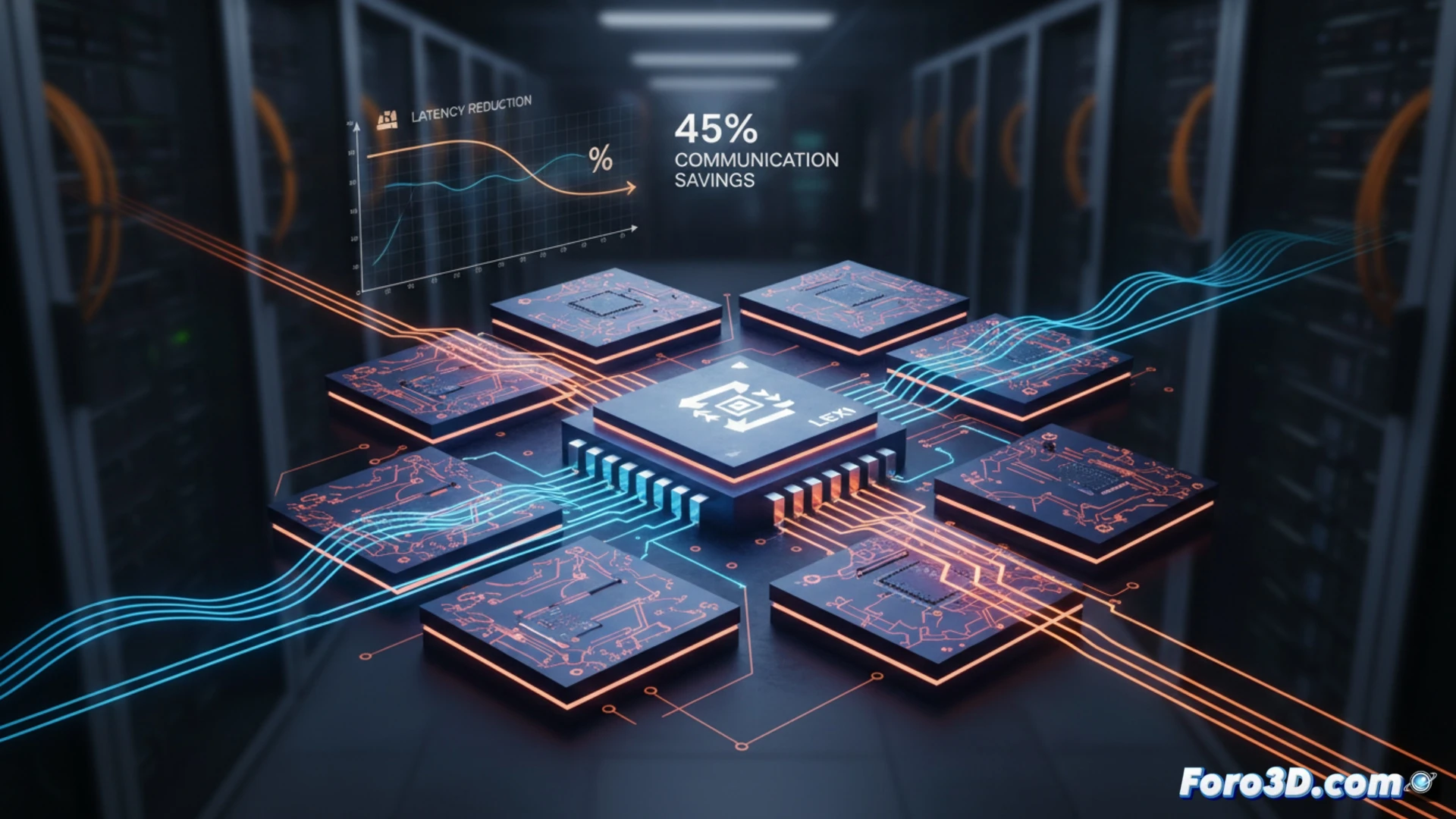

L'inferenza nei modelli di linguaggio grandi (LLM) è ostacolata dal collo di bottiglia nel movimento dei dati tra chiplet. Poiché questi modelli utilizzano prevalentemente il formato BF16, un'analisi rivela che i flussi di esponenti possiedono un'entropia molto bassa, inferiore a 3 bit, il che li rende altamente comprimibili. Presentiamo LEXI, uno schema di compressione senza perdite per esponenti basato su Huffman, che agisce direttamente nella rete su chip (NoC). Comprimendo attivazioni, cache e pesi, LEXI riduce la comunicazione e la latenza totale di inferenza tra il 33-45% e il 30-35%, rispettivamente, in architetture omogenee di chiplet, con un costo di area ed energia minimo.

Architettura e Implementazione del Codec LEXI nella NoC 🧠

LEXI si integra direttamente nei router della rete su chip. Piccoli codec si collocano nelle porte di ingresso e uscita, comprimendo e decomprimendo gli esponenti dei dati BF16 sul momento. La chiave sta nella sua implementazione hardware efficiente: utilizza decodificatori basati su tabelle di ricerca (LUT) multilinea che mantengono la larghezza di banda massima del collegamento, evitando che la compressione introduca ritardi. I pesi vengono memorizzati compressi in memoria e decompressi proprio prima del calcolo nel nucleo tensor. Fabbricato in tecnologia GF da 22 nm, l'overhead di questo sistema è di solo 0.09% in area e consumo energetico, un costo marginale per un guadagno sostanziale nelle prestazioni del sistema.

Impatto sul Futuro del Design 3D di Semiconduttori per IA 🚀

LEXI trascende una semplice tecnica di compressione; rappresenta un cambio di paradigma nel co-design di software e hardware per IA. Attaccando la ridondanza inerente nei formati numerici a livello del collegamento dati, permette architetture di chiplet più scalabili ed efficienti. Questo approccio mitiga uno dei maggiori limitanti attuali: la saturazione della larghezza di banda di interconnessione. Per il nicchio della microfabbricazione 3D, LEXI stabilisce un precedente chiaro: l'innovazione non sta solo nello stackare più transistor o chiplet, ma nell'ottimizzare intelligentemente ogni bit che viaggia tra loro, sbloccando nuove vette di prestazioni nell'inferenza di LLM.

Come può la tecnica di compressione degli esponenti LEXI ottimizzare il trasferimento dei dati tra chiplet per ridurre la latenza nell'inferenza di LLM?

(PD: simulare una wafer da 200mm è come fare una pizza: tutti vogliono un pezzo)