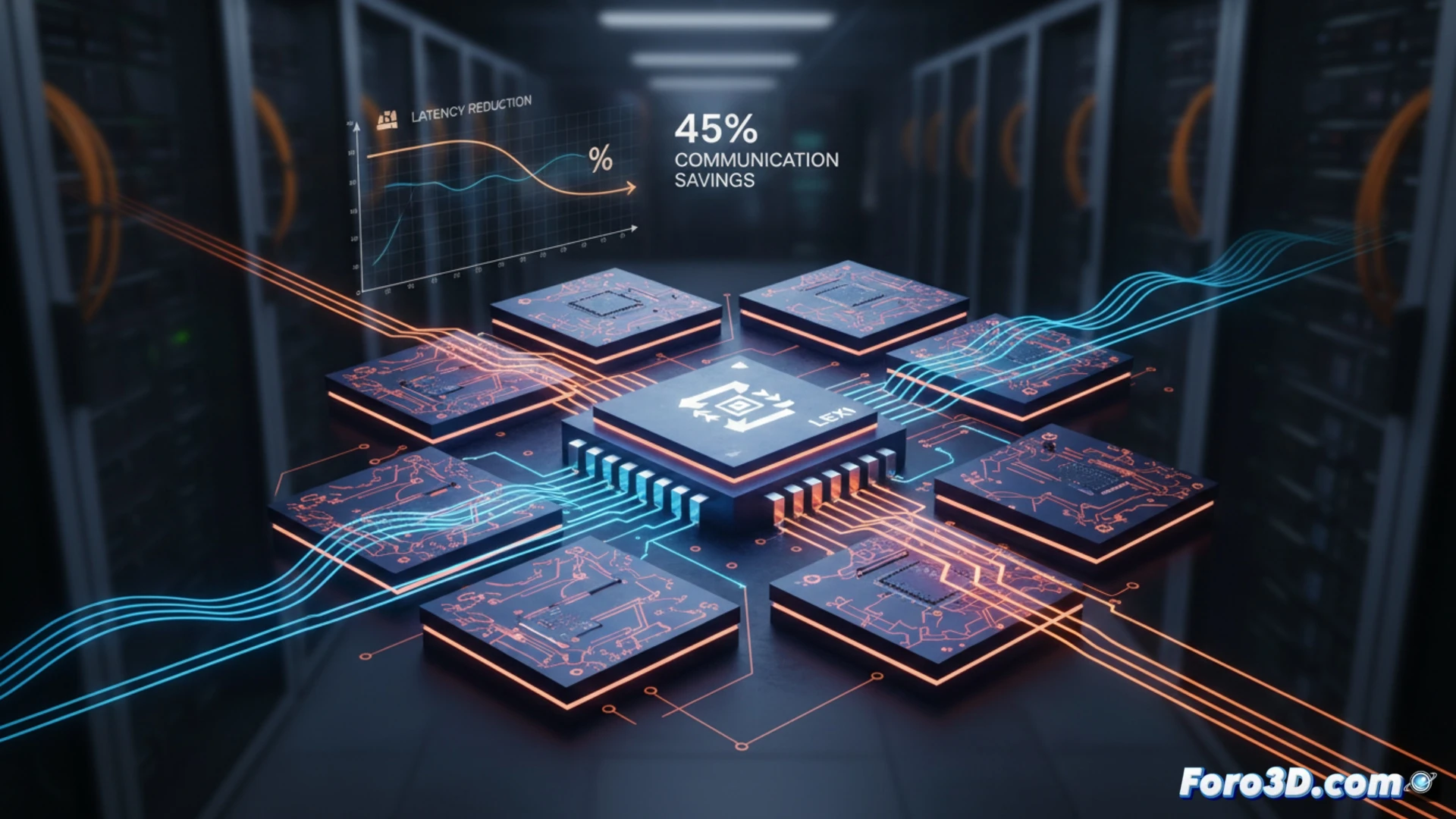

बड़े भाषा मॉडल (LLM) में अनुमान गणना चिपलेट्स के बीच डेटा आंदोलन के गले के बोतल द्वारा बाधित होती है। चूंकि ये मॉडल मुख्य रूप से BF16 प्रारूप का उपयोग करते हैं, एक विश्लेषण से पता चलता है कि एक्सपोनेंट्स के प्रवाह की एंट्रॉपी बहुत कम, 3 बिट्स से कम होती है, जो उन्हें अत्यधिक संपीड़नीय बनाती है। हम LEXI प्रस्तुत करते हैं, एक हफमैन-आधारित हानिरहित संपीड़न योजना एक्सपोनेंट्स के लिए जो चिप पर नेटवर्क (NoC) में सीधे कार्य करती है। सक्रियणों, कैश और वेट्स को संपीड़ित करके, LEXI संचार और कुल अनुमान गणना की latencia को क्रमशः 33-45% और 30-35% तक कम करता है, चिपलेट्स की समरूप वास्तुकलाओं में, न्यूनतम क्षेत्र और ऊर्जा लागत के साथ।

NoC में LEXI कोडेक की वास्तुकला और कार्यान्वयन 🧠

LEXI चिप पर नेटवर्क के राउटर्स में सीधे एकीकृत होता है। छोटे कोडेक इनपुट और आउटपुट पोर्ट्स पर स्थित होते हैं, जो BF16 डेटा के एक्सपोनेंट्स को तुरंत संपीड़ित और असंपीड़ित करते हैं। इसकी कुंजी इसकी कुशल हार्डवेयर कार्यान्वयन में है: यह मल्टीलाइन लुक-अप टेबल (LUT) आधारित डिकोडर का उपयोग करता है जो लिंक के अधिकतम बैंडविड्थ को बनाए रखता है, जिससे संपीड़न में देरी न हो। वेट्स को मेमोरी में संपीड़ित रूप में संग्रहीत किया जाता है और टेंसर कोर में गणना से ठीक पहले असंपीड़ित किए जाते हैं। 22 nm GF तकनीक में निर्मित, इस सिस्टम का ओवरहेड केवल 0.09% क्षेत्र और ऊर्जा उपभोग में है, जो सिस्टम प्रदर्शन में पर्याप्त लाभ के लिए एक सीमांत लागत है।

AI के लिए अर्धचालक 3D डिजाइन के भविष्य पर प्रभाव 🚀

LEXI एक साधारण संपीड़न तकनीक से परे है; यह AI के लिए सॉफ्टवेयर और हार्डवेयर के सह-डिजाइन में एक परिवर्तनकारी बदलाव का प्रतिनिधित्व करता है। डेटा लिंक स्तर पर संख्यात्मक प्रारूपों में निहित अतिरेकता पर हमला करके, यह अधिक स्केलेबल और कुशल चिपलेट वास्तुकलाओं को सक्षम बनाता है। यह दृष्टिकोण वर्तमान सबसे बड़े बाधाओं में से एक को कम करता है: इंटरकनेक्शन बैंडविड्थ की संतृप्ति। 3D माइक्रोफैब्रिकेशन के क्षेत्र के लिए, LEXI एक स्पष्ट मिसाल स्थापित करता है: नवाचार न केवल अधिक ट्रांजिस्टर या चिपलेट्स को ढेर करने में है, बल्कि उनके बीच यात्रा करने वाले प्रत्येक बिट को बुद्धिमानी से अनुकूलित करने में है, जो LLM अनुमान गणना में नए प्रदर्शन स्तरों को अनलॉक करता है।

एक्सपोनेंट संपीड़न तकनीक LEXI LLM अनुमान गणना में latencia को कम करने के लिए चिपलेट्स के बीच डेटा हस्तांतरण को कैसे अनुकूलित कर सकती है?

(PD: 200mm वेफर का सिमुलेशन पिज्जा बनाने जैसा है: हर कोई एक टुकड़ा चाहता है)