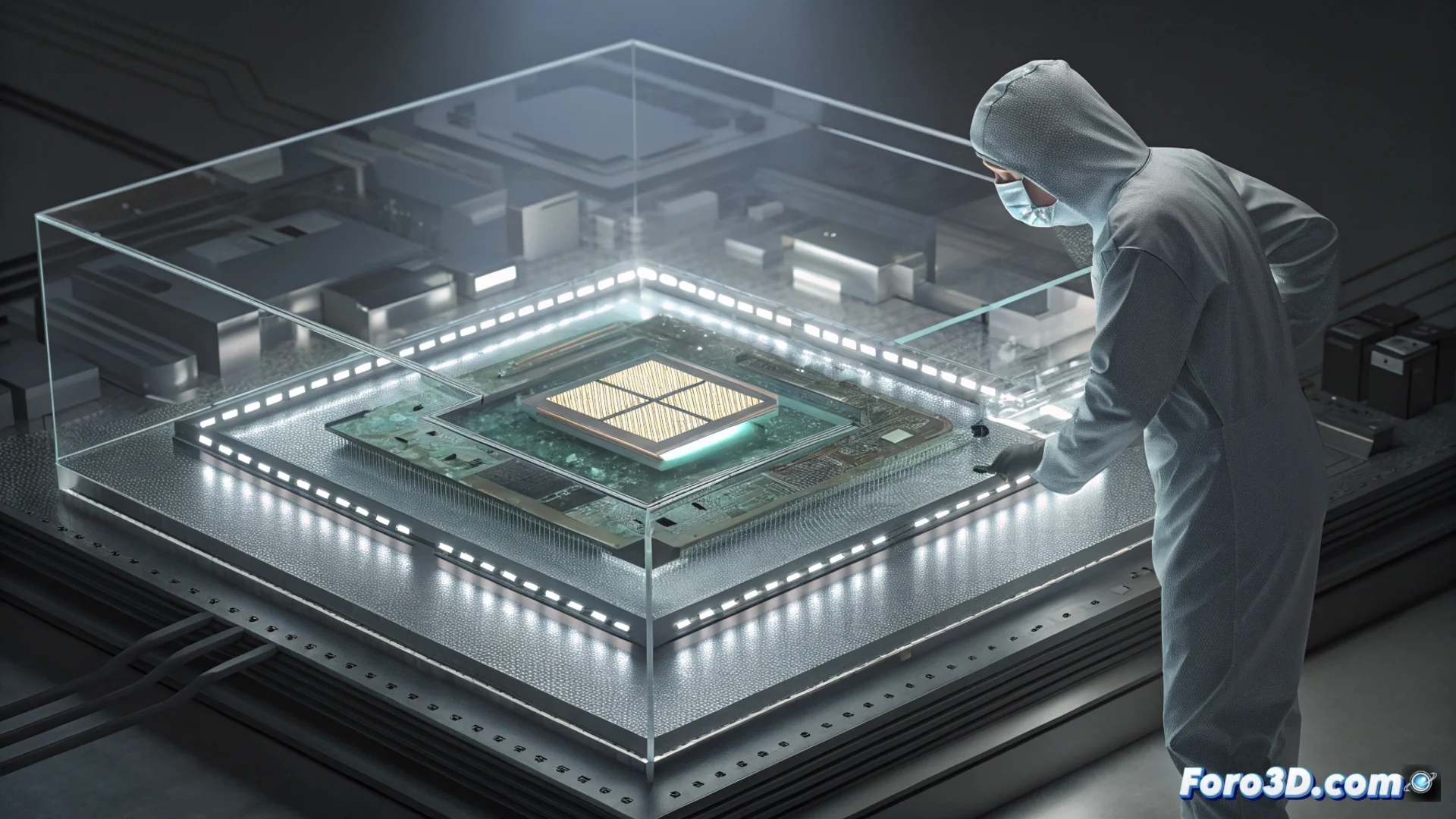

Imec GPU के स ubstr ate पर HBM मेमोरी को सीधे एकीकृत करता है

इवेंट IEDM में, अनुसंधान केंद्र Imec ने एक प्रगति का खुलासा किया जो कम्प्यूटिंग एक्सेलेरेटर्स के निर्माण के तरीके को फिर से परिभाषित कर सकता है। उनका प्रोटोटाइप HBM मेमोरी को एक ग्राफिक्स प्रोसेसिंग यूनिट के सिलिकॉन स ubstr ate पर सीधे निर्माण करने का प्रदर्शन करता है। यह विधि, जिसे HBM on GPU कहा जाता है, आज GPU को स्टैक्ड मेमोरी मॉड्यूल्स से जोड़ने वाले सिलिकॉन इंटरमीडिएट घटक को दबाने का प्रयास करती है। परिणाम संकेतों के लिए छोटा रास्ता है, जो प्रदर्शन को बढ़ावा देता है और ऊर्जा उपयोग को अनुकूलित करता है, कृत्रिम बुद्धिमत्ता और उच्च प्रदर्शन कम्प्यूटिंग के लिए दो स्तंभ। 🚀

तकनीकी आधार: TSMC का 3D SoIC

यह विकास शून्य से नहीं शुरू होता। यह TSMC की 3D SoIC एकीकरण तकनीक पर आधारित है। इसे परीक्षण करने के लिए, Imec ने एक टेस्ट चिप बनाई जो 3 नैनोमीटर N3 नोड पर निर्मित लॉजिक डाई को चार स्टैक्ड DRAM डाइज़ से जोड़ती है। जादू कनेक्शन में होता है: वे केवल 6 माइक्रोमीटर की न्यूनतम ऊंचाई वाले तांबे के माइक्रोबंप्स का उपयोग करते हैं। यह हाइब्रिड बॉन्डिंग प्रक्रिया विशाल इंटरकनेक्शन घनत्व प्राप्त करती है, जो 10,000 से अधिक कनेक्शन प्रति वर्ग मिलीमीटर को पार करती है। अंतिम संरचना अधिक कॉम्पैक्ट है और पारंपरिक HBM समाधानों की तुलना में अधिक कुशल दिखाई देती है जो निष्क्रिय इंटरपोज़र पर निर्भर करते हैं।

प्रोटोटाइप की मुख्य विशेषताएँ:- आर्किटेक्चर: N3 नोड पर एक लॉजिक डाई (GPU) जो चार स्टैक्ड मेमोरी DRAM डाइज़ से जुड़ा हुआ है।

- कनेक्शन तकनीक: 6µm तांबे के माइक्रोबंप्स जो उच्च घनत्व वाली हाइब्रिड बॉन्डिंग की अनुमति देते हैं।

- मुख्य लाभ: सिलिकॉन इंटरपोज़र को हटा देता है, डिज़ाइन को सरल बनाता है और विद्युत मार्गों को छोटा करता है।

ग्राफिक्स प्रोसेसर के स ubstr ate पर मेमोरी को सीधे एकीकृत करना सिस्टम डिज़ाइन को सरल बनाता है और पैकेजिंग की जटिलता को कम करता है।

सीधी बॉन्डिंग के लाभ और बाधाएँ

मेमोरी और लॉजिक को एक ही स ubstr ate पर जोड़ना ठोस लाभ लाता है। सिस्टम के डिज़ाइन को सरल बनाना और पैकेजिंग की जटिलता को कम करना पहले हैं। इंटरकनेक्शन मार्गों को नाटकीय रूप से छोटा करके, संकेत कम कम होते हैं और कम