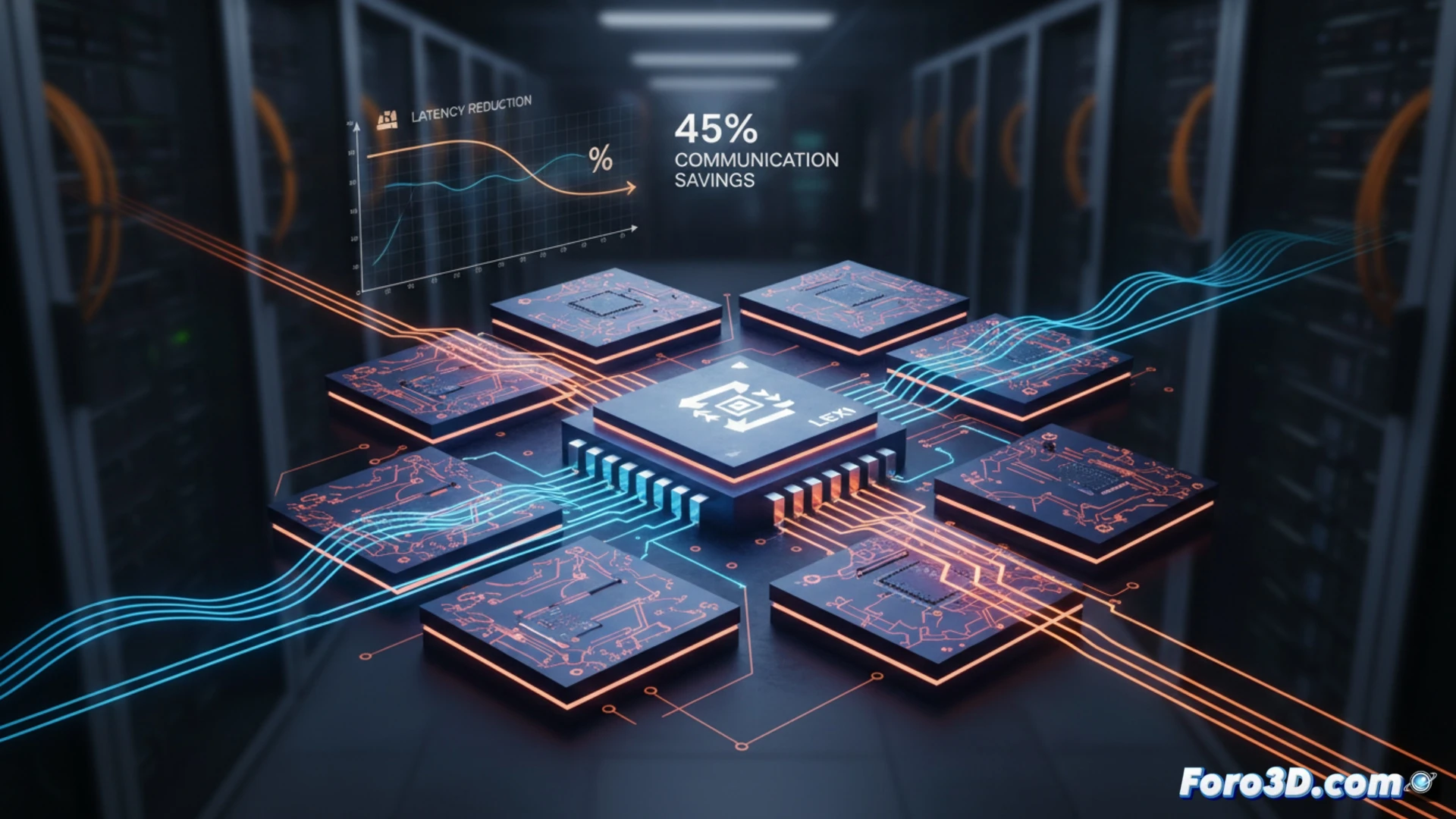

L'inférence dans les modèles de langage larges (LLM) est entravée par le goulot d'étranglement dans le mouvement des données entre chiplets. Étant donné que ces modèles utilisent principalement le format BF16, une analyse révèle que les flux d'exposants possèdent une entropie très faible, inférieure à 3 bits, ce qui les rend hautement compressibles. Nous présentons LEXI, un schéma de compression sans perte pour exposants basé sur Huffman, qui agit directement dans le réseau sur puce (NoC). En compressant les activations, les caches et les poids, LEXI réduit la communication et la latence totale d'inférence de 33-45 % et 30-35 % respectivement, dans des architectures homogènes de chiplets, avec un coût en surface et en énergie minimal.

Architecture et Implémentation du Codec LEXI dans la NoC 🧠

LEXI s'intègre directement dans les routeurs du réseau sur puce. De petits codecs sont situés dans les ports d'entrée et de sortie, compressant et décompressant les exposants des données BF16 en temps réel. La clé réside dans son implémentation matérielle efficace : elle utilise des décodeurs basés sur des tables de recherche (LUT) multilignes qui maintiennent la bande passante maximale du lien, évitant que la compression introduise des retards. Les poids sont stockés compressés en mémoire et décompressés juste avant le calcul dans le noyau tenseur. Fabriqué en technologie GF de 22 nm, le surcoût de ce système n'est que de 0,09 % en surface et en consommation énergétique, un coût marginal pour un gain substantiel en performance du système.

Impact sur l'Avenir de la Conception 3D de Semi-conducteurs pour l'IA 🚀

LEXI transcende une simple technique de compression ; elle représente un changement de paradigme dans le co-design logiciel et matériel pour l'IA. En attaquant la redondance inhérente dans les formats numériques au niveau du lien de données, elle permet des architectures de chiplets plus scalables et efficaces. Cette approche atténue l'une des plus grandes limitations actuelles : la saturation de la bande passante d'interconnexion. Pour le niche de la microfabrication 3D, LEXI établit un précédent clair : l'innovation ne réside pas seulement dans l'empilement de plus de transistors ou de chiplets, mais dans l'optimisation intelligente de chaque bit qui voyage entre eux, débloquant de nouvelles performances en inférence de LLMs.

Comment la technique de compression d'exposants LEXI peut-elle optimiser le transfert de données entre chiplets pour réduire la latence dans l'inférence de LLMs ?

(PD: simular une oblea de 200mm es como hacer una pizza: todo el mundo quiere un trozo)