Omni, l'interface de mémoire ouverte qui défie la DDR5

Dans le paysage de la technologie de mémoire, émerge un nouveau concurrent : l'Interface de Mémoire Ouverte (OMI). Ce protocole d'interconnexion série à haute vitesse se positionne comme une alternative directe aux normes traditionnelles de JEDEC, comme l'omniprésent DDR5. Son design fondamental vise à révolutionner la façon dont les systèmes accèdent aux données. 🚀

Un pont universel pour la mémoire

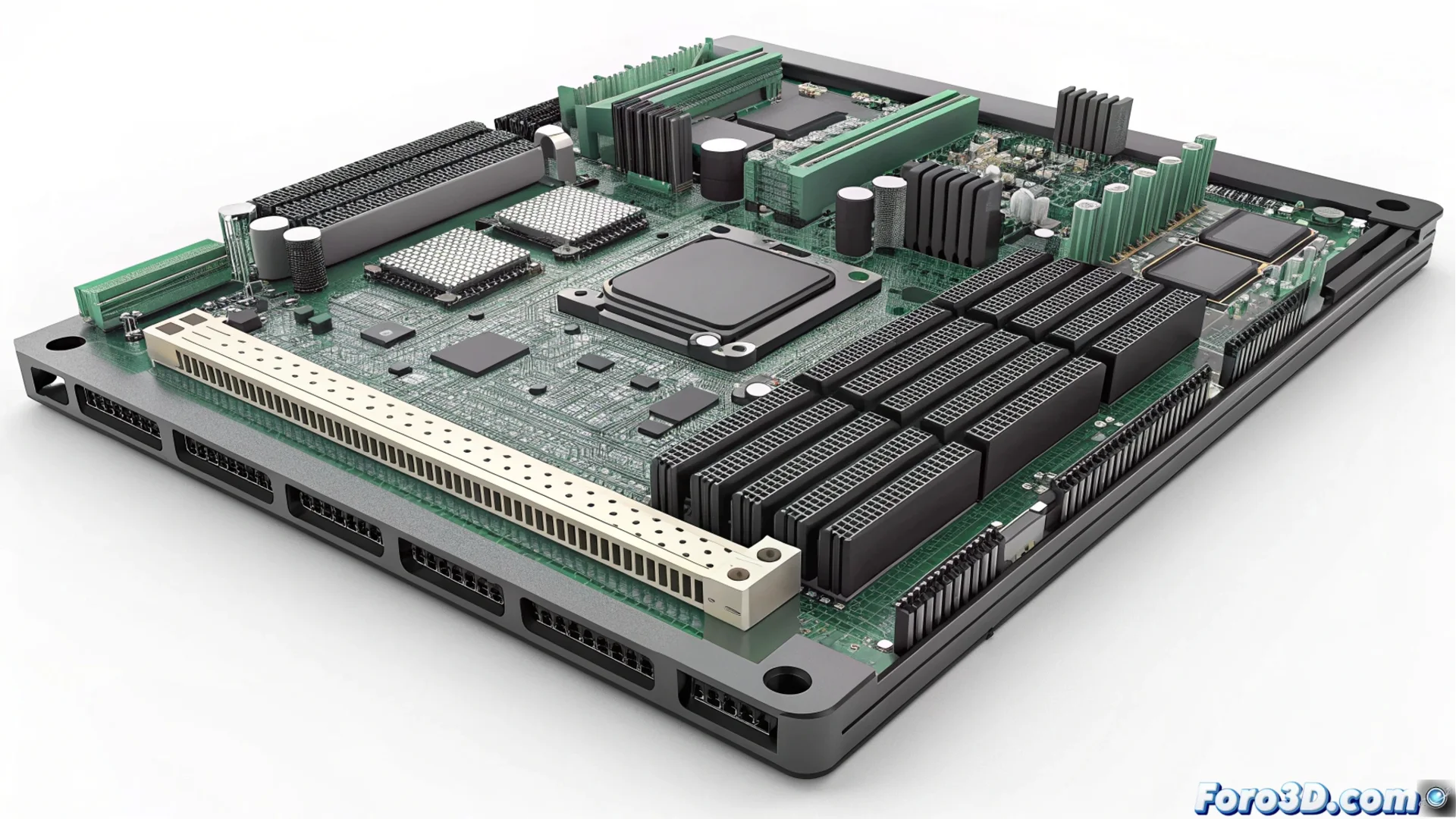

Le cœur de l'OMI est un contrôleur qui se situe dans le propre chip du processeur ou dans un interposeur très proche. Ce composant agit comme un traducteur et un gestionnaire, communiquant avec les modules de mémoire via un bus série. L'innovation clé réside dans le fait que ces modules, appelés DIMM OMI, peuvent intégrer physiquement différentes technologies de puces de mémoire. Le contrôleur s'occupe d'adapter les requêtes du processeur au protocole natif utilisé par chaque puce, qu'il s'agisse de DDR, GDDR ou même HBM.

Avantages clés de cette approche :- Liberté de conception : Les ingénieurs ne dépendent pas d'une seule norme de mémoire physique pour l'ensemble du système.

- Réduire la latence : L'architecture de liaison directe et la gestion efficace visent à minimiser les retards d'accès.

- Augmenter la bande passante effective : Optimise le flux de données pour les exigences les plus élevées.

L'OMI fonctionne comme un pont flexible entre le processeur et la mémoire, découplant l'interface logique de la technologie physique sous-jacente.

Optimiser pour l'IA et la computation haute performance

Ce protocole trouve sa raison d'être dans des environnements spécialisés comme les serveurs pour l'intelligence artificielle (IA) et la computation haute performance (HPC). Dans ces domaines, les besoins en mémoire sont divers et spécifiques : certaines tâches requièrent une bande passante monumentale, d'autres priorisent une capacité énorme et d'autres exigent une latence minimale. L'OMI permet de choisir le type de mémoire le plus adapté pour chaque sous-système au sein de la même plateforme.

Applications pratiques dans un système hétérogène :- Utiliser des modules avec mémoire HBM à haute bande passante pour accélérer les cœurs d'un GPU ou d'un accélérateur d'IA.

- Employer des modules avec mémoire DDR de grande capacité pour le pool de mémoire principal du processeur central (CPU).

- Mélanger les technologies selon la phase de la charge de travail, optimisant ainsi les performances et l'efficacité.

Le défi d'une norme ouverte

La proposition d'une norme ouverte qui unifie l'écosystème complexe des interfaces de mémoire est, en théorie, très attractive. Elle promet de simplifier, d'abaisser les coûts et de rendre plus efficaces les conceptions de systèmes. Cependant, l'histoire de l'industrie technologique montre que les bonnes intentions se heurtent souvent aux intérêts commerciaux et aux investissements établis des grands fabricants. Le succès de l'OMI dépendra de son adoption et de sa capacité à démontrer des avantages tangibles et convaincants face à l'infrastructure bien ancrée de JEDEC. La voie est ouverte, mais pas exempte d'obstacles. ⚡