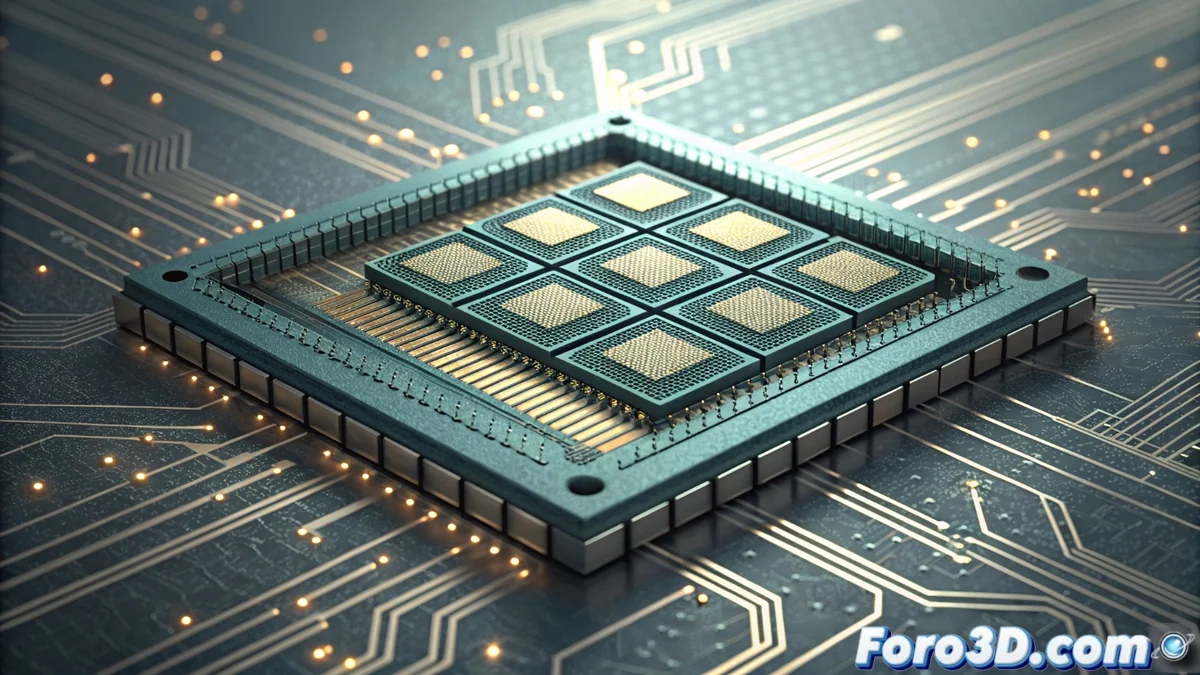

L'architecture PIM : traitement en mémoire comme révolution du hardware

La conception du hardware connaît une transformation radicale avec l'émergence de l'architecture PIM (Processing In Memory). Ce paradigme remet en question des décennies de conventions en plaçant la logique de calcul directement au sein des modules de mémoire, qu'il s'agisse de DDR ou des piles avancées HBM (High Bandwidth Memory). Le principe est d'exécuter les opérations là où les données résident, éliminant le besoin de déplacer de grandes quantités d'informations à travers le bus du système vers le CPU ou le GPU. Ce changement promet de résoudre le goulot d'étranglement le plus critique de l'informatique moderne. 🚀

Avantages transformateurs et cas d'usage

L'impact de PIM se manifeste dans deux dimensions clés : performance brute et efficacité énergétique. En réduisant drastiquement le mouvement des données, on consomme une fraction de l'énergie, un progrès crucial pour les centres de données et la superinformatique. Les applications gérant de grands ensembles de données en sont les principales bénéficiaires. Ici, la latence s'effondre et la bande passante effective se multiplie.

Domaines d'application clés :- Apprentissage automatique et IA : Accélère l'entraînement des modèles et l'inférence en traitant les matrices de données directement en mémoire.

- Analyse de bases de données : Accélère les requêtes complexes et les opérations de filtrage et de tri sur de grands volumes d'informations.

- Simulation scientifique et rendu : Optimise les tâches nécessitant un accès intensif aux tampons et aux géométries complexes, courant en graphismes 3D et CFD.

L'ironie finale est que, après des décennies à optimiser les CPU pour déplacer les données plus vite, la solution semble être de ne pas les déplacer du tout.

Obstacles sur le chemin de l'adoption

Malgré son potentiel, la mise en œuvre de PIM n'est pas exempte de défis profonds. Elle nécessite une réinvention complète des hiérarchies de mémoire et du logiciel qui les gère. Les développeurs ont besoin de nouveaux modèles de programmation et d'outils pour exploiter ce traitement décentralisé.

Principaux défis à surmonter :- Complexité de conception : Intégrer une logique de calcul dans des puces de mémoire denses pose des problèmes de fabrication, de dissipation de chaleur et de fiabilité.

- Écosystème logiciel : Il faut de nouveaux compilateurs, bibliothèques et frameworks qui abstrayent la complexité du hardware pour les programmeurs.

- Architecture du système : La coordination entre le CPU, le GPU et les multiples unités PIM en mémoire nécessite de nouveaux designs d'interconnexion et de cohérence.

L'avenir et les implémentations actuelles

L'industrie avance déjà avec des prototypes et des premières solutions, signalant un chemin irréversible. Des entreprises comme Samsung avec ses mémoires HBM-PIM, et des géants comme AMD et Intel avec des architectures explorant des concepts similaires, mènent cette hybridation entre mémoire et traitement. Ce virage conceptuel, que Von Neumann n'avait probablement pas anticipé, redéfinit les fondements de l'informatique, priorisant la proximité des données sur la vitesse de leur transport. L'avenir du hardware sera, sans doute, plus intégré et efficace. 💡