Intel Foundry détaille son matériel spécialisé pour l'IA et le HPC

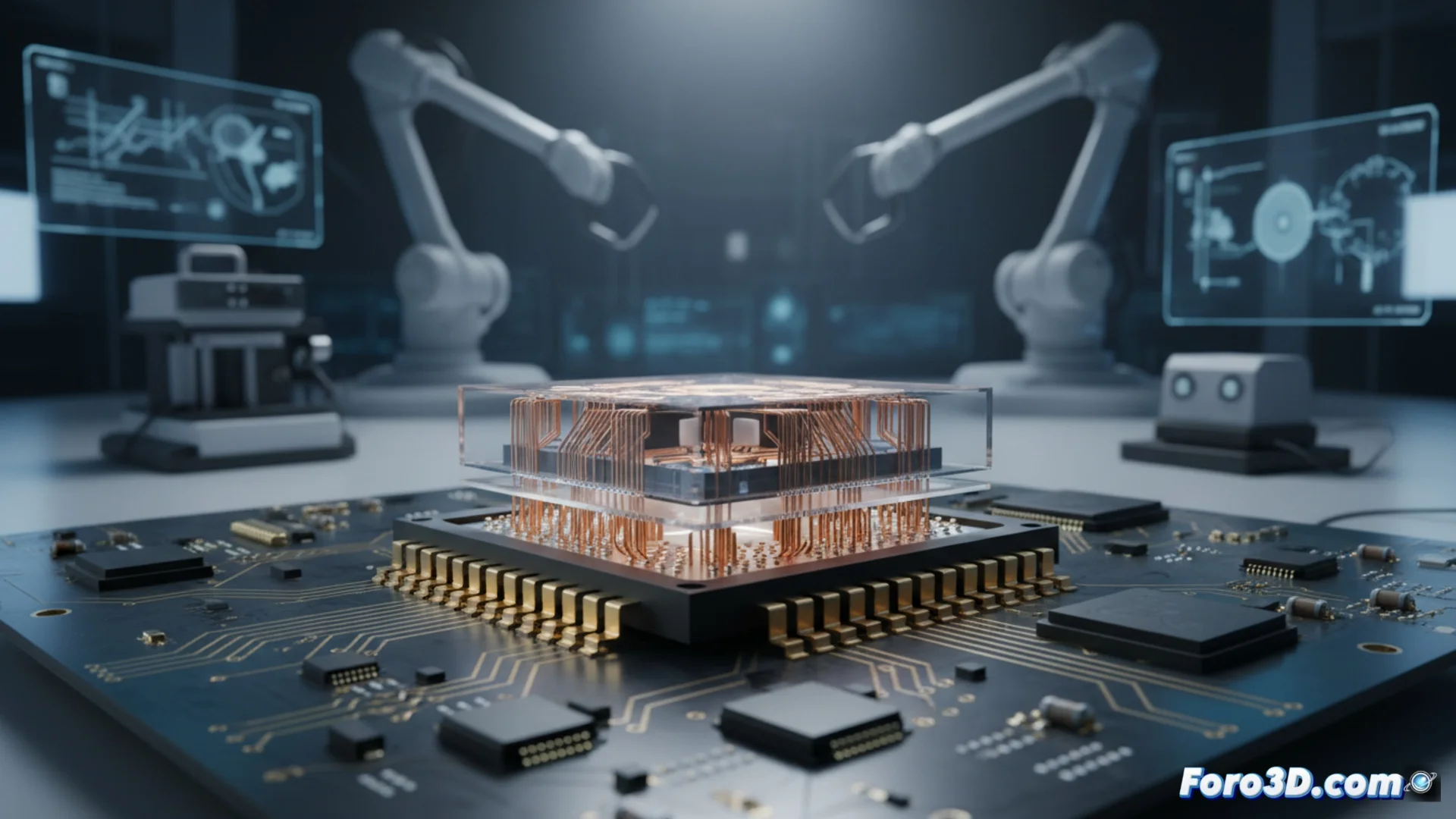

La division de fabrication d'Intel a révélé un rapport technique dans lequel elle explique comment elle conçoit et produit des composants physiques dédiés à l'exécution de tâches d'intelligence artificielle et de calcul de haute performance. Le document est accompagné de la présentation d'une puce de validation qui sert à démontrer sa capacité actuelle à intégrer plusieurs éléments dans un seul dispositif. 🧠

Options de fabrication et d'empaquetage avancé

Le matériel divulgué spécifie les alternatives de production qu'Intel Foundry met à disposition de ses clients. Cela inclut des données sur des nœuds de fabrication de pointe, comme l'Intel 18A, et sur des méthodes pour combiner plusieurs chiplets ou fragments de silicium. L'objectif de ces solutions est de construire des systèmes plus puissants et plus efficaces, en unissant des cœurs de calcul, une mémoire rapide et des éléments de connexion dans un seul paquet.

Détails clés du document :- Description des nœuds de processus les plus avancés disponibles.

- Technologies pour intégrer plusieurs chiplets de manière efficace.

- Approche pour créer des systèmes complets et optimisés dans un seul paquet.

La puce de test est une première étape cruciale pour valider les technologies avant de les produire à grande échelle.

Validation des capacités d'empaquetage en trois dimensions

Le prototype pour l'IA qu'Intel présente intègre plusieurs innovations fondamentales. Il utilise l'architecture PowerVia pour gérer la distribution d'énergie et la technologie Foveros Direct pour relier des puces en 3D en utilisant des connexions en cuivre. Cette stratégie permet d'empiler des composants, comme des processeurs et des modules de mémoire, pour raccourcir la distance parcourue par les données et ainsi optimiser à la fois les performances et la consommation énergétique.

Technologies implémentées dans la puce de test :- Architecture PowerVia pour une distribution d'énergie plus efficace.

- Foveros Direct pour des interconnexions 3D en cuivre de haute densité.

- Capacité d'empiler des composants et de réduire les latences.

Un avancement vers l'avenir commercial

Bien que le rapport technique soit étendu et détaillé, la puce de validation ne représente que la phase initiale de ce chemin. Il reste encore du chemin à parcourir pour que ces progrès se matérialisent en produits finaux qui arrivent sur le marché et que les utilisateurs puissent acquérir. Le document souligne l'engagement d'Intel à repousser les limites du matériel spécialisé pour les exigences computationnelles les plus exigeantes. ⚙️