OMI, the Open Memory Interface Challenging DDR5

In the memory technology landscape, a new contender emerges: the Open Memory Interface (OMI). This high-speed serial interconnection protocol positions itself as a direct alternative to JEDEC's traditional standards, such as the ubiquitous DDR5. Its fundamental design seeks to revolutionize how systems access data. 🚀

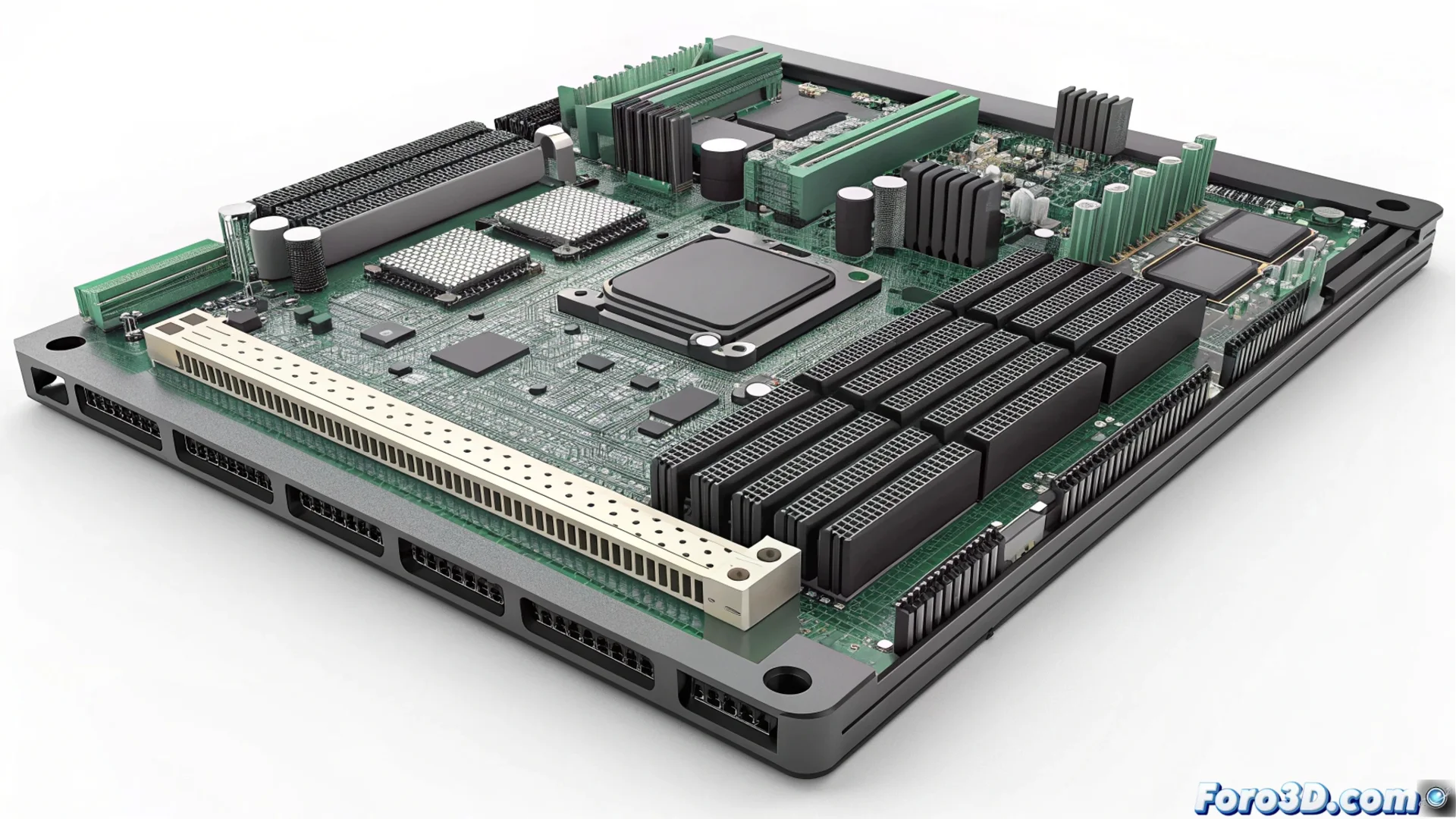

A Universal Bridge for Memory

The core of OMI is a controller located on the processor chip itself or in a very close interposer. This component acts as a translator and manager, communicating with memory modules through a serial bus. The key innovation lies in the fact that these modules, called OMI DIMMs, can physically integrate different memory chip technologies. The controller handles adapting the processor's requests to the native protocol used by each chip, whether DDR, GDDR, or even HBM.

Key advantages of this approach:- Design freedom: Engineers are not dependent on a single physical memory standard for the entire system.

- Reduce latency: The direct link architecture and efficient management aim to minimize access delays.

- Increase effective bandwidth: Optimizes data flow for the most demanding needs.

OMI functions as a flexible bridge between the processor and memory, decoupling the logical interface from the underlying physical technology.

Optimized for AI and High-Performance Computing

This protocol finds its raison d'être in specialized environments like servers for artificial intelligence (AI) and high-performance computing (HPC). In these fields, memory needs are diverse and specific: some tasks require monumental bandwidth, others prioritize enormous capacity, and others demand minimal latency. OMI allows choosing the most suitable memory type for each subsystem within the same platform.

Practical applications in a heterogeneous system:- Use modules with HBM memory for high bandwidth to accelerate GPU cores or an AI accelerator.

- Employ modules with DDR memory of large capacity for the central processor's (CPU) main memory pool.

- Mix technologies according to the workload phase, thus optimizing performance and efficiency.

The Challenge of an Open Standard

The proposal of an open standard that unifies the complex ecosystem of memory interfaces is, in theory, very attractive. It promises to simplify, reduce costs, and make system designs more efficient. However, the history of the technology industry shows that good intentions often face commercial interests and established investments from major manufacturers. OMI's success will depend on its adoption and whether it can demonstrate tangible and compelling advantages over JEDEC's entrenched infrastructure. The path is open, but not without obstacles. ⚡