OMI, die offene Speicherschnittstelle, die DDR5 herausfordert

Im Panorama der Speichertechnologie taucht ein neuer Konkurrent auf: die Offene Speicherschnittstelle (OMI). Dieses Hochgeschwindigkeits-Seriell-Protokoll positioniert sich als direkte Alternative zu den traditionellen JEDEC-Standards wie dem allgegenwärtigen DDR5. Sein grundlegendes Design zielt darauf ab, zu revolutionieren, wie Systeme auf Daten zugreifen. 🚀

Eine universelle Brücke für Speicher

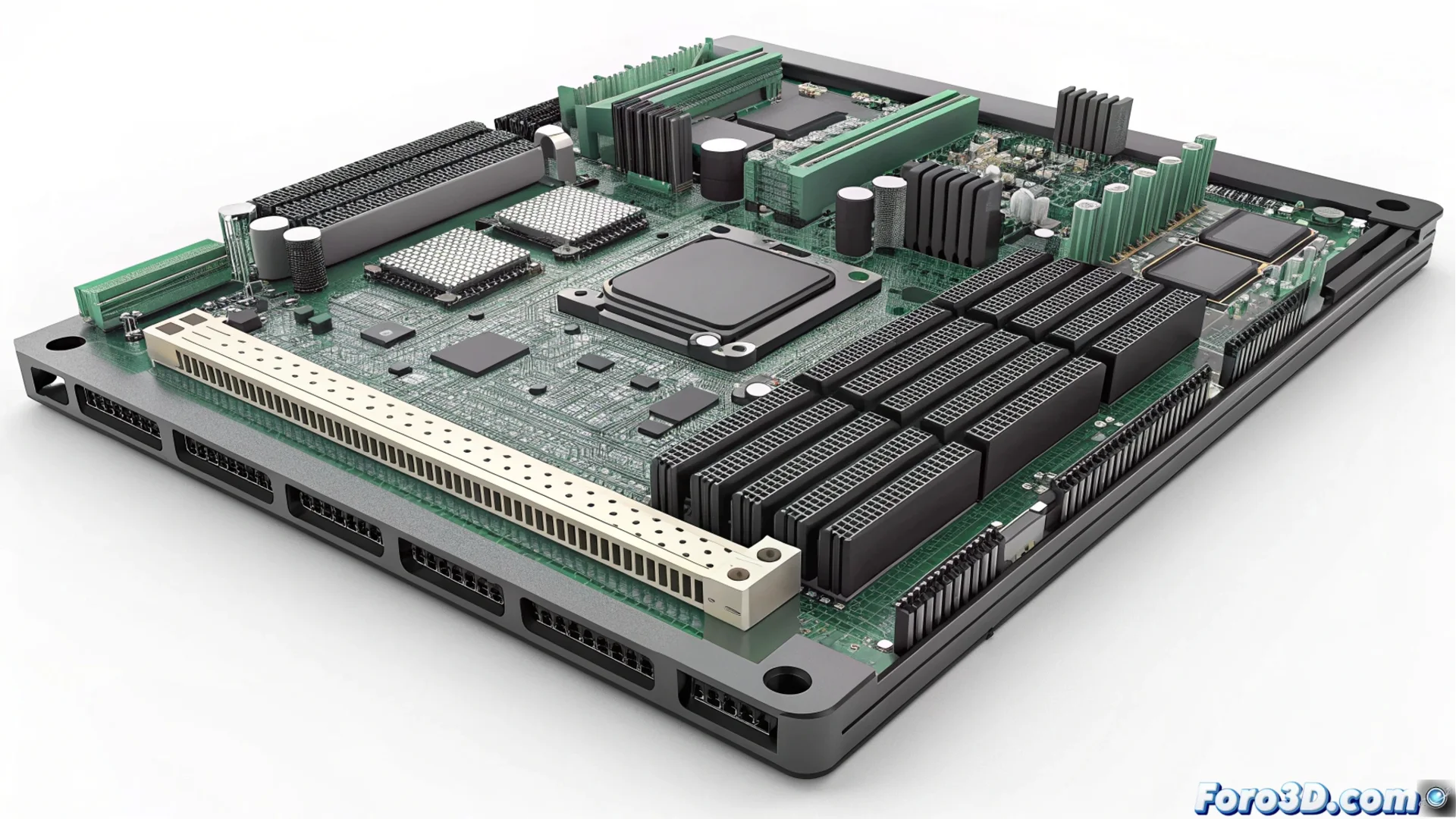

Der Kern von OMI ist ein Controller, der sich direkt auf dem Prozessorchip oder in unmittelbarer Nähe befindet. Diese Komponente fungiert als Übersetzer und Manager und kommuniziert mit den Speichermodulen über einen Seriellen Bus. Die Schlüsselinnovation liegt darin, dass diese Module, genannt OMI-DIMM, physisch unterschiedliche Speicherchip-Technologien integrieren können. Der Controller übernimmt die Anpassung der Prozessor-Anfragen an das native Protokoll jedes Chips, sei es DDR, GDDR oder sogar HBM.

Schlüsselvorteile dieses Ansatzes:- Designfreiheit: Die Ingenieure sind nicht auf einen einzigen physischen Speicherstandard für das gesamte System angewiesen.

- Latenz reduzieren: Die Direkte-Verbindungsarchitektur und die effiziente Verwaltung zielen darauf ab, Verzögerungen beim Zugriff zu minimieren.

- Effektive Bandbreite erhöhen: Optimiert den Datenfluss für die anspruchsvollsten Anforderungen.

OMI fungiert als flexible Brücke zwischen Prozessor und Speicher und entkoppelt die logische Schnittstelle von der zugrunde liegenden physischen Technologie.

Optimierung für KI und Hochleistungsrechnen

Dieses Protokoll findet seinen Sinn in spezialisierten Umgebungen wie Servern für Künstliche Intelligenz (KI) und Hochleistungsrechnen (HPC). In diesen Bereichen sind die Speicheranforderungen vielfältig und spezifisch: Einige Aufgaben erfordern eine monumentale Bandbreite, andere priorisieren eine riesige Kapazität und andere verlangen eine minimale Latenz. OMI ermöglicht die Auswahl des am besten geeigneten Speichertyps für jedes Subsystem innerhalb derselben Plattform.

Praktische Anwendungen in einem heterogenen System:- Verwendung von Modulen mit HBM-Speicher hoher Bandbreite, um die Kerne einer GPU oder eines KI-Beschleunigers zu beschleunigen.

- Einsatz von Modulen mit DDR-Speicher großer Kapazität für den Hauptspeicherpool des zentralen Prozessors (CPU).

- Mischung von Technologien je nach Phase der Arbeitslast, um so Leistung und Effizienz zu optimieren.

Die Herausforderung eines offenen Standards

Der Vorschlag eines offenen Standards, der das komplexe Ökosystem der Speicherschnittstellen vereinheitlicht, ist theoretisch sehr attraktiv. Er verspricht, Systemdesigns zu vereinfachen, zu verbilligen und effizienter zu machen. Allerdings zeigt die Geschichte der Technologiebranche, dass gute Absichten oft auf kommerzielle Interessen und etablierte Investitionen großer Hersteller stoßen. Der Erfolg von OMI hängt von seiner Adoption ab und davon, ob es greifbare und überzeugende Vorteile gegenüber der fest verwurzelten JEDEC-Infrastruktur nachweisen kann. Der Weg ist offen, aber nicht ohne Hindernisse. ⚡