Intel Foundry detailliert seine spezialisierte Hardware für KI und HPC

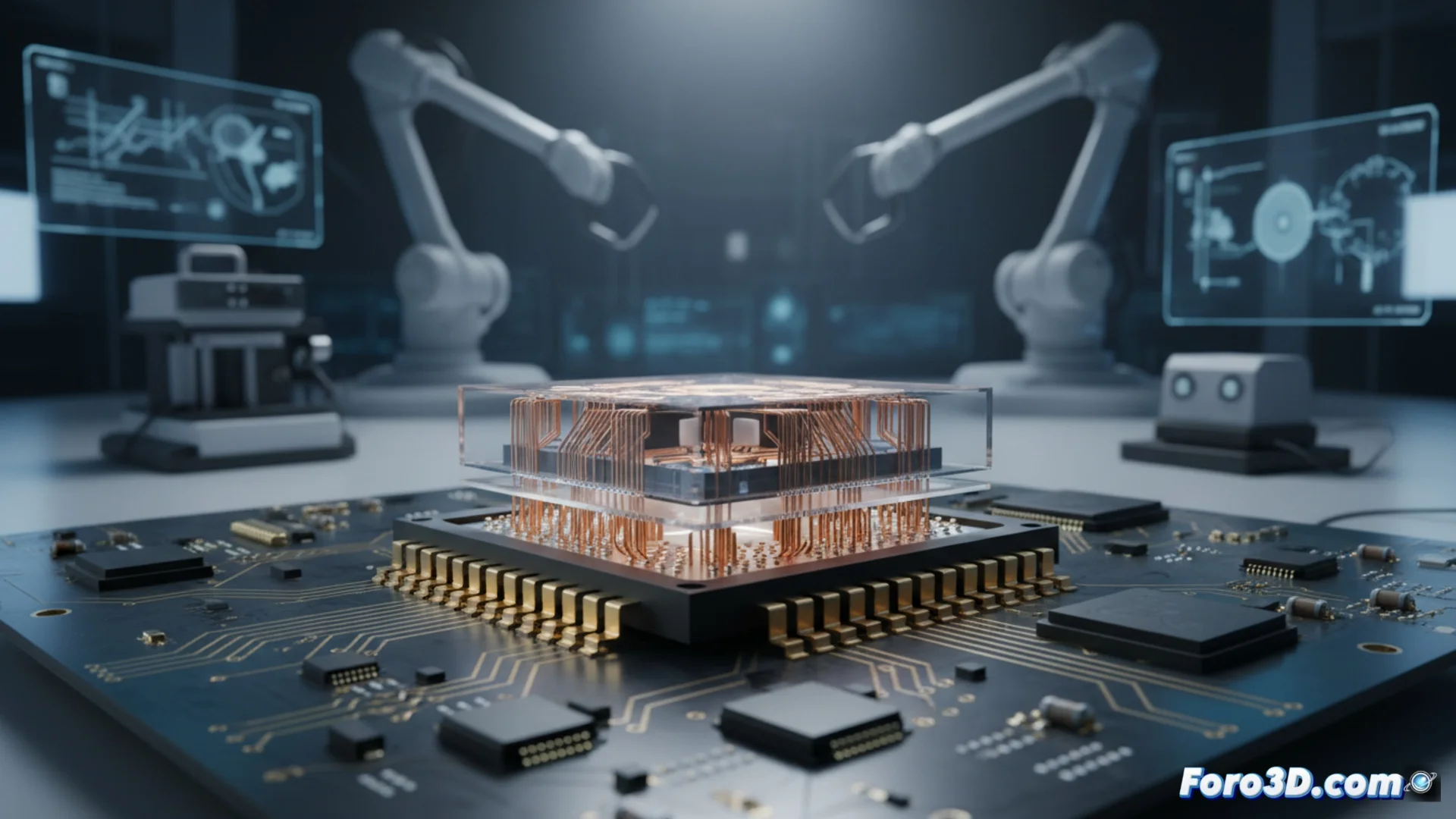

Die Fertigungssparte von Intel hat einen technischen Bericht veröffentlicht, in dem erklärt wird, wie sie physische Komponenten für die Ausführung von Aufgaben der künstlichen Intelligenz und des Hochleistungsrechnens konzipiert und produziert. Das Dokument wird von der Vorstellung eines Validierungs-Chips begleitet, der die aktuelle Fähigkeit demonstriert, mehrere Elemente in einem einzigen Gerät zu integrieren. 🧠

Fertigungs- und fortschrittliche Verpackungsoptionen

Das veröffentlichte Material spezifiziert die Produktionsalternativen, die Intel Foundry seinen Kunden zur Verfügung stellt. Hierzu gehören Daten zu Spitzen-Fertigungsknoten wie Intel 18A und Methoden zur Kombination mehrerer Chiplets oder Siliziumfragmente. Das Ziel dieser Lösungen ist es, leistungsstärkere und effizientere Systeme zu bauen, indem Rechenkernen, schnellem Speicher und Verbindungselementen in einem einzigen Paket zusammengeführt werden.

Wichtige Details des Dokuments:- Beschreibung der fortschrittlichsten verfügbaren Prozessknoten.

- Technologien zur effizienten Integration mehrerer Chiplets.

- Fokus auf die Erstellung vollständiger und optimierter Systeme in einem einzigen Paket.

Der Testchip ist ein entscheidender erster Schritt zur Validierung von Technologien vor der großskaligen Produktion.

Validierung der dreidimensionalen Verpackungsfähigkeiten

Das für KI vorgestellte Prototyp von Intel integriert mehrere grundlegende Innovationen. Es verwendet die Architektur PowerVia zur Verwaltung der Stromverteilung und die Technologie Foveros Direct zur Verbindung von Chips in 3D mit Kupferverbindungen. Diese Strategie ermöglicht das Stapeln von Komponenten wie Prozessoren und Speichermodulen, um die Datenstrecke zu verkürzen und so sowohl die Leistung als auch den Energieverbrauch zu optimieren.

Im Testchip implementierte Technologien:- PowerVia-Architektur für eine effizientere Stromversorgung.

- Foveros Direct für hochdichte 3D-Kupferverbindungen.

- Fähigkeit, Komponenten zu stapeln und Latenzen zu reduzieren.

Ein Fortschritt hin zu kommerziellen Produkten

Obwohl der technische Bericht umfangreich und detailliert ist, stellt der Validierungs-Chip nur die anfängliche Phase dieses Weges dar. Es bleibt noch ein langer Weg, bis diese Fortschritte in finale Produkte münden, die auf den Markt kommen und von Nutzern erworben werden können. Das Dokument unterstreicht das Engagement von Intel, die Grenzen der spezialisierten Hardware für die anspruchsvollsten Rechenanforderungen zu vorantreiben. ⚙️