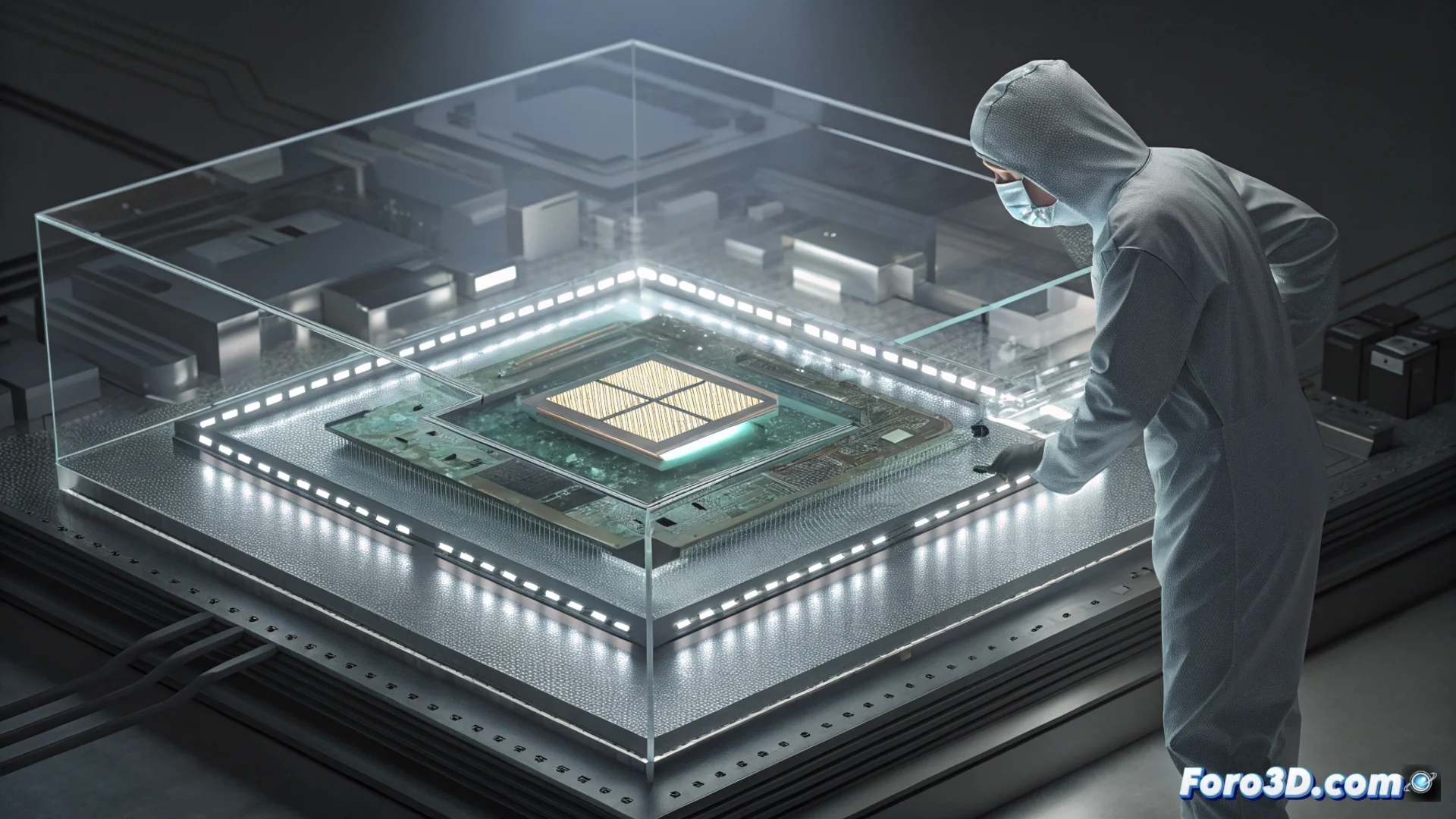

Imec 将 HBM 内存直接集成到 GPU 基板上

在 IEDM 活动中,研究机构 Imec 公布了一项可能重新定义计算加速器构建方式的突破。其原型展示了在图形处理单元的硅基板上直接制造HBM 内存。这种被称为HBM on GPU的方法旨在消除当今连接 GPU 与堆叠内存模块的中间硅组件。结果是信号路径更短,从而提升性能并优化能耗,这是人工智能和高性能计算的两大支柱。🚀

技术基础:TSMC 的 3D SoIC

这一开发并非从零开始。它依托 TSMC 的3D SoIC 集成技术。为了验证,Imec 创建了一个测试芯片,将一个在3 纳米 N3节点制造的逻辑芯片与四个堆叠的DRAM 芯片连接起来。魔力在于连接:它们使用高度仅为6 微米的铜微凸点。这种混合键合工艺实现了极高的互连密度,超过每平方毫米 10,000 个连接。最终结构更紧凑,并有望比依赖被动中介层的传统 HBM 解决方案更高效。

原型关键特性:- 架构: 一个 N3 节点逻辑芯片(GPU)连接到四个堆叠的 DRAM 内存芯片。

- 连接技术: 6µm 铜微凸点,实现高密度混合键合。

- 主要优势: 消除硅中介层,简化设计并缩短电气路径。

将内存直接集成到图形处理器基板上简化了系统设计并降低了封装复杂性。

直接键合的益处与障碍

将内存和逻辑集成在同一基板上带来了切实优势。简化系统设计和降低封装复杂性是首要的。通过大幅缩短互连路径,信号衰减更少,并需要更少