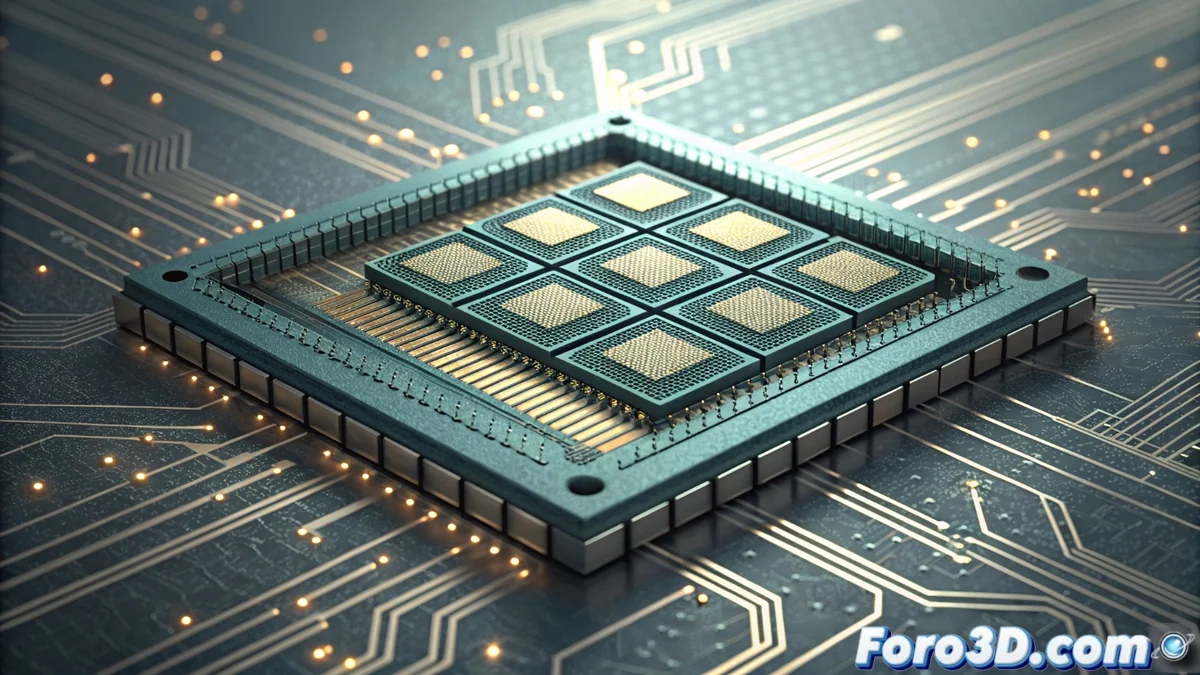

PIM 架构:内存处理作为硬件革命

硬件设计正经历一场激进的变革,随着PIM 架构(内存处理)的出现。这一范式挑战了数十年的传统,将计算逻辑直接置于内存模块内部,无论是DDR还是先进的HBM(高带宽内存)堆栈。其原理是在数据驻留的位置执行操作,消除将海量信息通过系统总线移动到 CPU 或 GPU 的需求。这一变革有望解决现代计算中最关键的瓶颈。🚀

变革性优势和用例

PIM 的影响体现在两个关键维度:原始性能和能效。通过大幅减少数据移动,能耗仅为原来的几分之一,这对数据中心和超级计算至关重要。处理大型数据集的应用是主要受益者。在此,延迟急剧下降,有效带宽成倍增加。

关键应用领域:- 机器学习和 AI:通过直接在内存中处理数据矩阵,加速模型训练和推理。

- 数据库分析:加速复杂查询以及在大规模信息中的过滤和排序操作。

- 科学模拟和渲染:优化需要密集访问缓冲区和复杂几何体的任务,这在 3D 图形和 CFD 中很常见。

最终的讽刺是,在数十年优化 CPU 以更快移动数据之后,解决方案似乎是不移动数据。

采用道路上的障碍

尽管潜力巨大,PIM 的实施并非没有深刻挑战。它需要完全重塑内存层次结构和软件管理机制。开发者需要新的编程模型和工具来利用这种去中心化处理。

主要挑战:- 设计复杂性:在密集内存芯片中集成计算逻辑,会带来制造、散热和可靠性问题。

- 软件生态系统:需要新的编译器、库和框架来为程序员抽象硬件复杂性。

- 系统架构:CPU、GPU 与内存中多个 PIM 单元之间的协调,需要新的互连和一致性设计。

未来和当前实现

行业已推进原型和首批解决方案,标志着不可逆转的道路。像Samsung的HBM-PIM内存,以及AMD和Intel等巨头探索类似概念的架构,正在引领内存与处理的混合。这一概念转向,恐怕冯·诺伊曼未曾预料,它重新定义了计算基础,优先考虑数据的接近性而非传输速度。硬件的未来无疑将更集成和高效。💡