- 14/10/2025 17:20

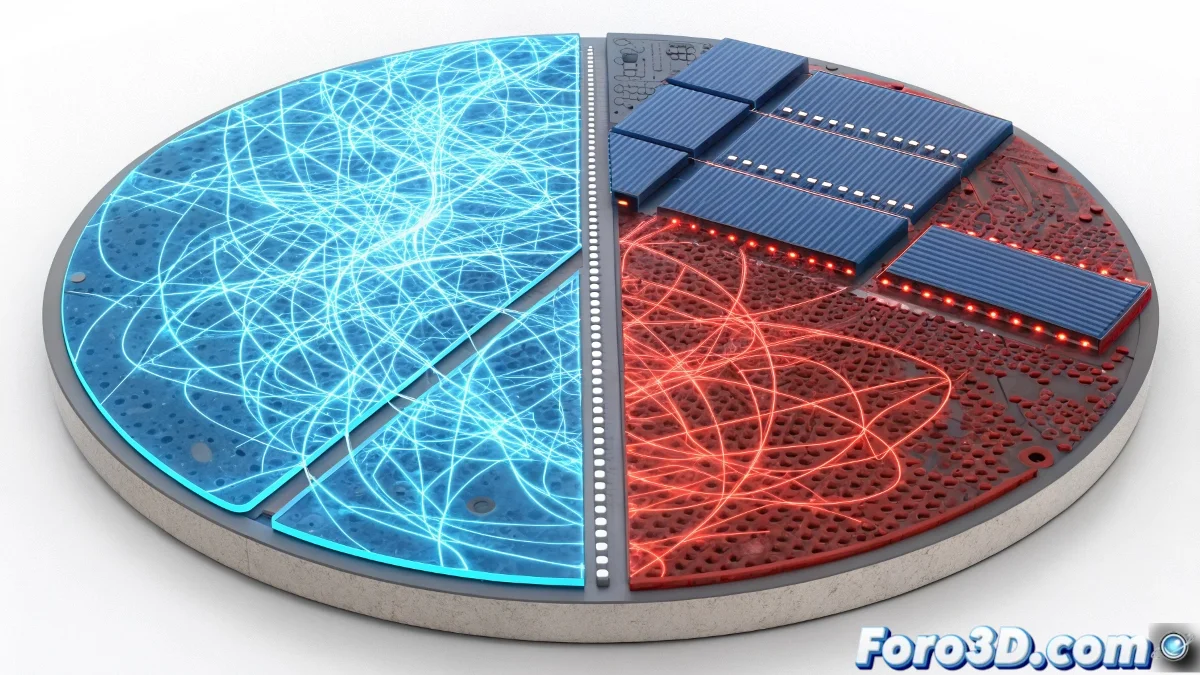

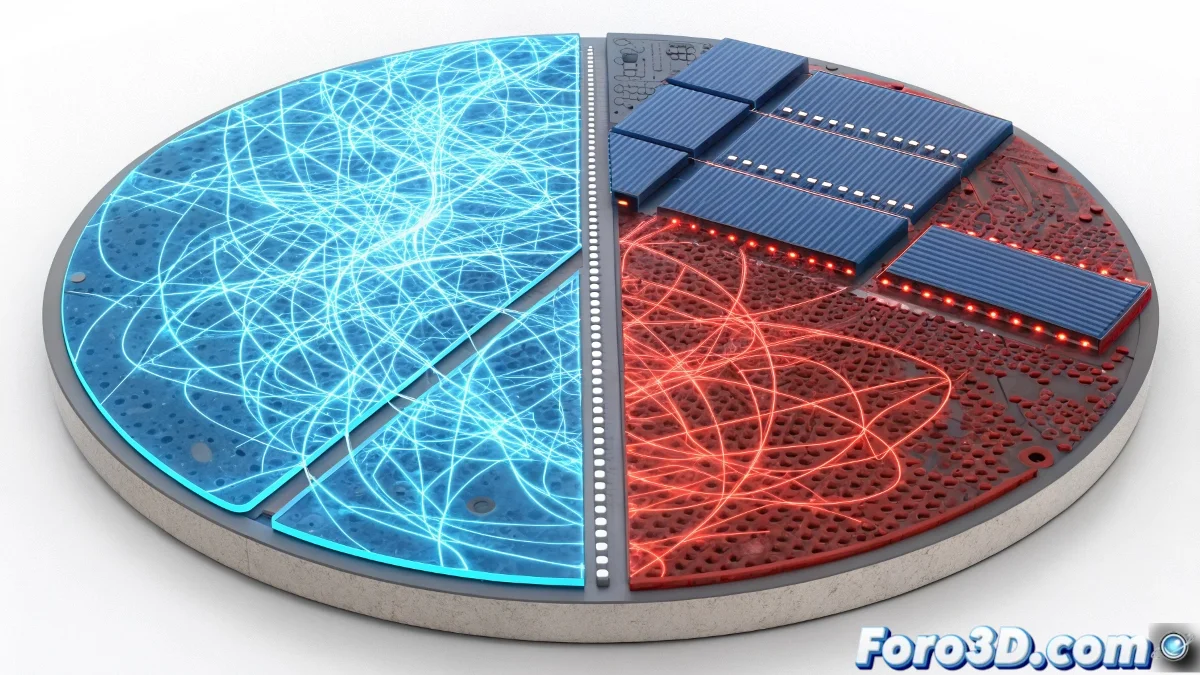

Es una tecnología de Intel que redefine la forma en que se suministra energía a los transistores dentro de un chip. A diferencia de los métodos tradicionales, donde las conexiones eléctricas se sitúan en la parte superior de la oblea junto con las señales de datos, PowerVia traslada las rutas de alimentación a la parte posterior del chip. Este enfoque, conocido como backside power delivery, permite separar las redes de energía y de señal, reduciendo interferencias y mejorando la eficiencia general del circuito.

Ventajas frente al diseño convencional

Al mover las líneas de energía a la parte trasera del chip, PowerVia libera espacio en la parte frontal para los transistores y sus interconexiones de señal. Esto permite una mayor densidad de componentes y una reducción en la resistencia eléctrica, lo que se traduce en menos pérdidas de energía y menor generación de calor. Además, el suministro directo desde la parte posterior mejora la estabilidad del voltaje y reduce el ruido eléctrico, dos factores esenciales para alcanzar frecuencias más altas con menor consumo.

Impacto en el rendimiento y la fabricación

PowerVia complementa a RibbonFET dentro del nodo Intel 18A, creando una sinergia entre rendimiento y eficiencia energética. Los primeros resultados internos muestran una mejora de hasta un 6 % en frecuencia y una reducción significativa en la caída de voltaje. Esta arquitectura representa uno de los mayores avances de Intel en décadas, ya que optimiza la alimentación del chip sin necesidad de aumentar el tamaño ni el consumo energético.

Mientras los ingenieros celebran la energía que ahora llega por detrás, los transistores probablemente estén felices de recibir electricidad sin tanto tráfico por encima de sus cabezas.

Ventajas frente al diseño convencional

Al mover las líneas de energía a la parte trasera del chip, PowerVia libera espacio en la parte frontal para los transistores y sus interconexiones de señal. Esto permite una mayor densidad de componentes y una reducción en la resistencia eléctrica, lo que se traduce en menos pérdidas de energía y menor generación de calor. Además, el suministro directo desde la parte posterior mejora la estabilidad del voltaje y reduce el ruido eléctrico, dos factores esenciales para alcanzar frecuencias más altas con menor consumo.

Impacto en el rendimiento y la fabricación

PowerVia complementa a RibbonFET dentro del nodo Intel 18A, creando una sinergia entre rendimiento y eficiencia energética. Los primeros resultados internos muestran una mejora de hasta un 6 % en frecuencia y una reducción significativa en la caída de voltaje. Esta arquitectura representa uno de los mayores avances de Intel en décadas, ya que optimiza la alimentación del chip sin necesidad de aumentar el tamaño ni el consumo energético.

Mientras los ingenieros celebran la energía que ahora llega por detrás, los transistores probablemente estén felices de recibir electricidad sin tanto tráfico por encima de sus cabezas.