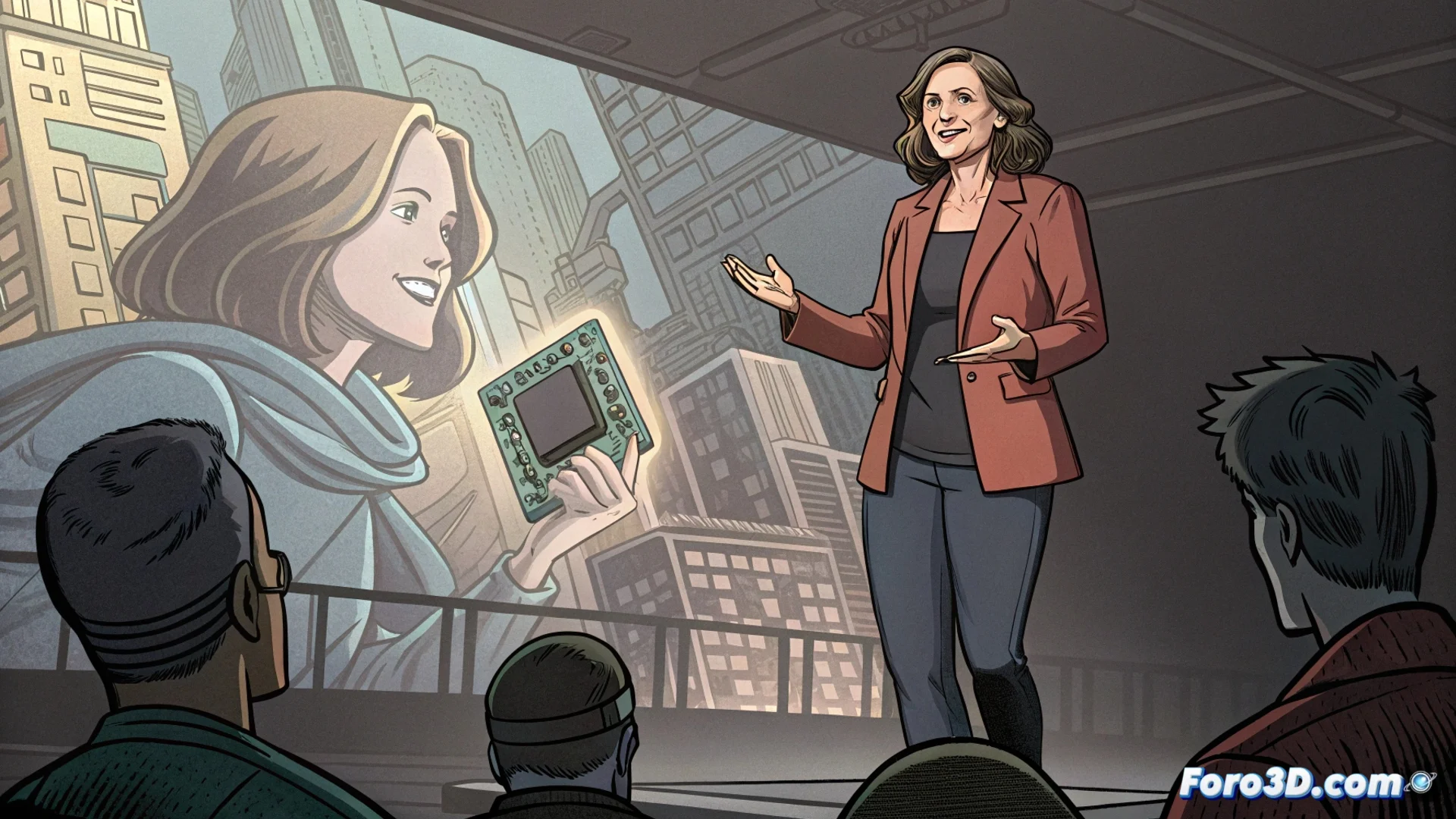

Lisa Su apresenta o processador EPYC Venice com Zen 6 na CES 2026

O palco da CES em Las Vegas foi testemunha de um anúncio chave para o setor de servidores. Lisa Su, diretora executiva da AMD, revelou dois produtos estratégicos, destacando o novo processador EPYC Venice que implementa a arquitetura Zen 6. A revelação mais impactante foi seu design físico radical, que marca um ponto de inflexão em como esses componentes são construídos. 🚀

Um design que rompe com a convenção térmica

O processador Venice foi mostrado sem sua tampa de distribuição térmica (IHS), um elemento padrão na indústria. Essa decisão de expor os chiplets não é um simples gesto visual, mas uma escolha técnica profunda. Ao eliminar essa camada intermediária, a AMD busca que o sistema de refrigeração faça contato direto com as fontes de calor primárias.

Vantagens chave do design aberto:- Reduzir a resistência térmica: Eliminar a interface entre o silício e o dissipador permite que o calor seja transferido de maneira mais eficiente.

- Habilitar empacotamento sofisticado: Essa abordagem é fundamental para usar técnicas de montagem mais avançadas, que a AMD não detalhou completamente.

- Otimizar para cargas sustentadas: O benefício direto é que o processador pode manter frequências de clock altas por mais tempo ou consumir menos energia para executar as mesmas tarefas.

No mundo dos servidores, mostrar o interior já não é de má educação, mas uma declaração de intenções técnicas.

A arquitetura Zen 6 e seu contexto competitivo

Este lançamento não se entende sem a base que fornece o Zen 6. A combinação desta nova microarquitetura com o método revolucionário de empacotamento está claramente direcionada a dominar o mercado de centros de dados e computação em nuvem, segmentos onde a eficiência e o desempenho por watt são críticos.

Objetivos estratégicos do projeto Venice:- Competir em alto desempenho: Posicionar-se frente a outras soluções para servidores com uma proposta técnica diferenciadora.

- Melhorar a gestão de energia: O design térmico superior está intrinsecamente ligado a gerenciar melhor a potência em ambientes de alta densidade.

- Adotar inovação de packaging: A apresentação sublinha que este passo é necessário para implementar a próxima geração de tecnologia de empacotamento, crucial para a evolução dos chips.

Uma declaração de princípios para a indústria

A apresentação de Lisa Su na CES 2026 transcende o lançamento de um produto. O processador EPYC Venice simboliza uma mudança de filosofia: priorizar a eficiência técnica extrema sobre as convenções de design. Ao expor o coração de silício, a AMD não só mostra um chip, mas desafia a indústria a repensar como construir hardware para os desafios computacionais do futuro. A mensagem é clara: na busca pelo desempenho, cada camada eliminada conta. 💡