Wafer-on-wafer bonding: a técnica de empacotamento 3D extrema

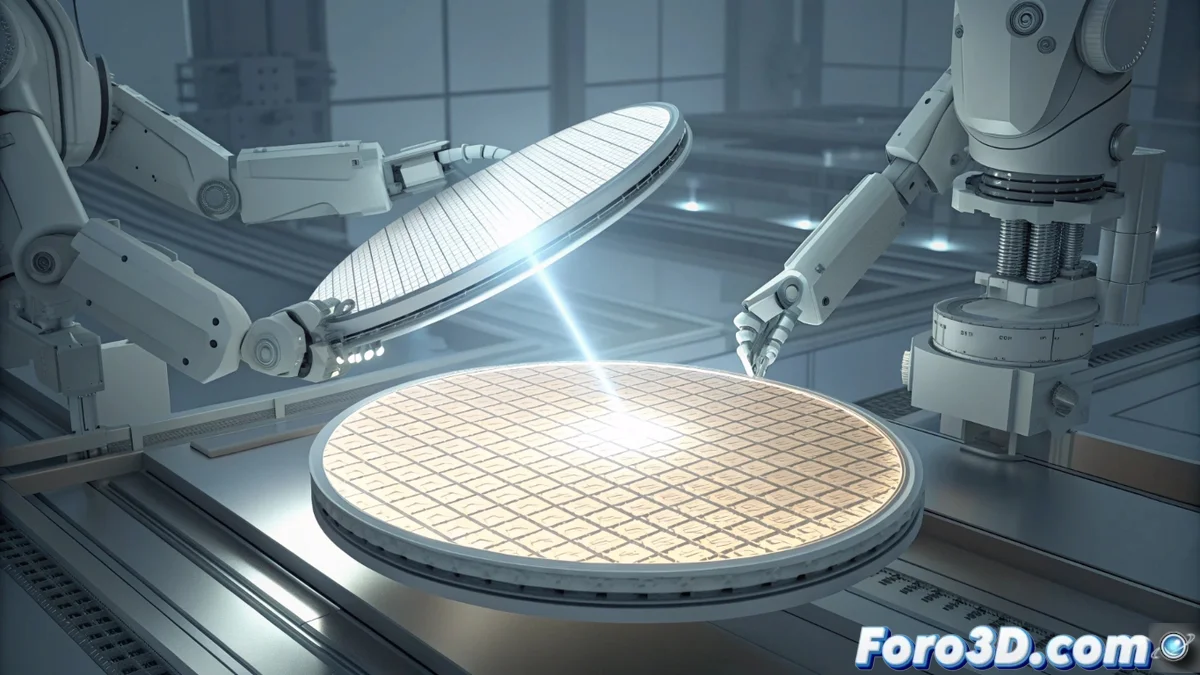

Na busca por maior potência e eficiência, a indústria de semicondutores avança para a terceira dimensão. Uma das metodologias mais radicais é o Wafer-on-Wafer (WoW) bonding, que funde duas obleas de silício completas antes de separá-las em chips individuais. Esse método contrasta com as abordagens tradicionais e habilita uma integração de sistemas sem precedentes. 🚀

O processo de união nanométrica

A técnica não empilha chips já cortados, mas opera em um nível anterior. Primeiro, processam-se duas obleas de forma independente, cada uma com seus próprios transistores e circuitos. Em seguida, um equipamento de alinhamento de alta precisão as posiciona cara a cara com exatidão nanométrica. A união permanente é obtida aplicando calor e pressão controlados, criando um bloco monolítico de silício. Dentro desse bloco, os canais elétricos entre as duas metades são incrivelmente densos e curtos. Somente após essa fusão, o bloco é cortado para obter os dispositivos 3D finais.

Vantagens chave do WoW bonding:- Densidade de interconexão extrema: Conectar no nível de oblea permite milhares de vezes mais vias de comunicação do que com microbumps.

- Rota de sinal ultra curta: Os dados viajam distâncias mínimas entre módulos, o que acelera a transferência e reduz o consumo de energia.

- Integração de sistema completo: Facilita unir, por exemplo, unidades de processamento lógico e bancos de memória de alta velocidade em um único dispositivo compacto.

O verdadeiro desafio não é unir as obleas, mas evitar que se colem de forma acidental durante a fabricação, um problema que todo engenheiro conhece muito bem.

Comparação com outras técnicas 3D

Métodos como o empilhamento de chips (Chip-on-Chip) ou o uso de Through-Silicon Vias (TSVs) têm limitações inerentes. Nesses casos, as conexões verticais (microbumps ou TSVs) são fisicamente maiores e mais separadas, criando um gargalo para a comunicação. O WoW bonding elimina esse obstáculo ao interconectar os transistores de uma oblea diretamente com os da outra em escala microscópica. Isso transforma como flui a informação entre os diferentes blocos funcionais de um sistema.

Diferenças principais:- Escala de conexão: WoW opera no nível de transistor/obleia, enquanto outras técnicas o fazem no nível de chip/empacotamento.

- Espaçamento entre vias: A densidade de interconexões no WoW é de ordens de magnitude superior.

- Processo de fabricação: WoW une antes de cortar, o que simplifica o manuseio e alinhamento de componentes extremamente pequenos.

Desafios e futuro da integração 3D

Implementar essa tecnologia não está isento de obstáculos. Além do risco de aderência prematura das obleas, são necessárias salas limpas com níveis de limpeza excepcionais e equipamentos de alinhamento de custo muito elevado. No entanto, a recompensa justifica o esforço: sistemas completos, mais rápidos e eficientes, empacotados em um espaço mínimo. Essa evolução é crucial para seguir a Lei de Moore e alimentar a próxima geração de computação, inteligência artificial e dispositivos móveis. O WoW bonding representa um salto conceitual em como construímos a eletrônica. 💡