Lyra:RISC-Vプロセッサ検証のための生成フレームワーク

RISC-Vプロセッサの複雑な設計を検証することは重要な課題です。ソフトウェアによる遅いシミュレーションに依存し、ランダムなテスト刺激を使用する従来の方法は、大きなボトルネックとなっています。Lyra は、この問題の根本を解決する革新的なソリューションとして登場し、AI を直接ワークフローに統合します。🚀

テスト生成のためのインテリジェントなアプローチ

盲目的な突然変異やランダムベクトルに頼る代わりに、Lyra は 専門の生成モデル である LyraGen を組み込んでいます。このモデルはプロセッサの命令セットアーキテクチャ(ISA)を深く理解しています。主要な機能は、ランダムな方法が見逃すハードウェア設計の複雑な動作やコーナーケースを探求するために特別に設計された、意味豊かで高品質な命令シーケンスを生成することです。

LyraGen の主な利点:- RISC-V 命令のセマンティクスを理解したテスト刺激を生成します。

- ハードウェアの複雑な内部状態を指向的に探索します。

- 単純なランダム性を意味のある命令シーケンスに置き換えます。

チップ設計に必要なのは、AI がどの命令を実行するのが興味深いかを説明することであり、ランダムにキーボードを叩いて何かが失敗するまで続けることではありません。

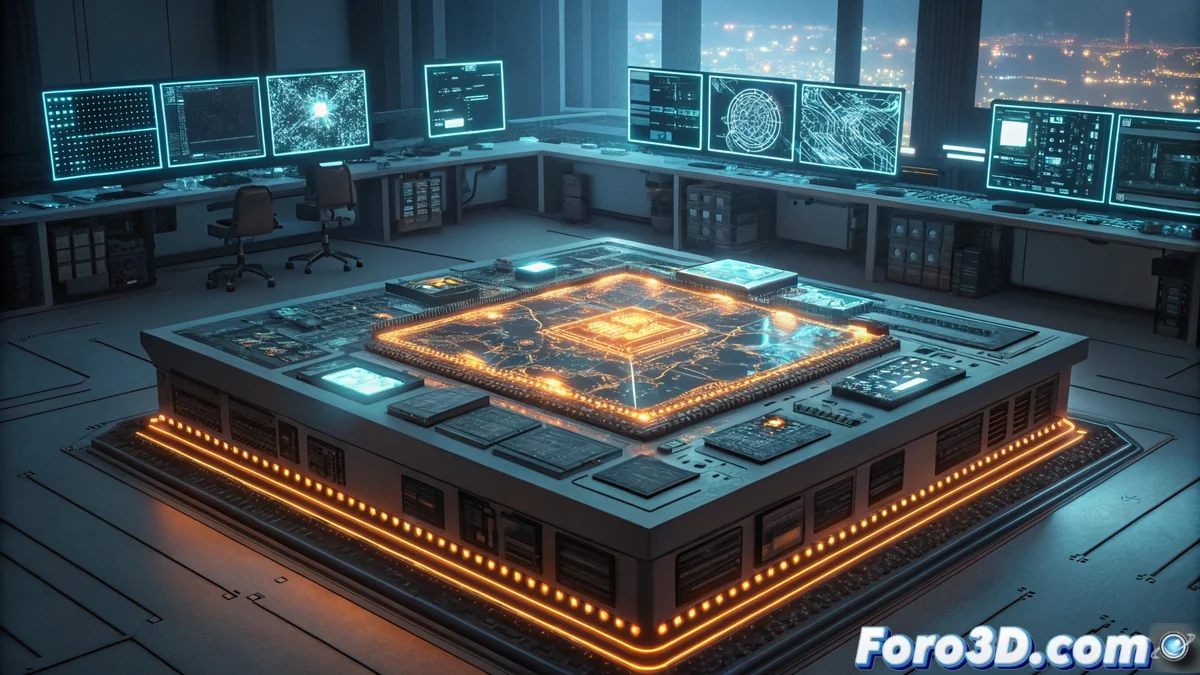

ハードウェア実行による大幅な高速化

Lyra のアーキテクチャは、テスト生成だけでなく実行も極めて高速です。システムは FPGA を備えた SoC 内で テスト対象ユニット とゴールドの 参照モデル を並列に実装します。このアプローチにより、ハードウェア速度で両者の違いを比較でき、劇的な高速化を実現します。また、ソフトウェアシミュレータでは不可能な大量のリアルタイムカバレッジメトリクスの収集を容易にします。

高速化された検証の結果:- FPGA のネイティブ速度で比較と検証を実行します。

- 包括的かつ効率的にカバレッジデータを収集します。

- LyraGen のインテリジェントな生成とハードウェアの速度を組み合わせます。

優位性を示す実証的な結果

Lyra を使った実験テストは、最先端の従来のソフトウェア検証器に対して定量的かつ大幅な改善を示しています。システムは 設計カバレッジを最大 1.27 倍向上 させ、より多くのエッジケースと重要な状態を発見します。速度に関しては、エンドツーエンドの検証プロセスを 107 〜 3343 倍 高速化します。もう一つの重要な利点は、一貫して低い収束難易度であり、これは複雑な設計の検証に必要な総コストと時間を直接削減します。✅