Intel、AI競争のためにHBM5搭載の巨大チップレットを設計

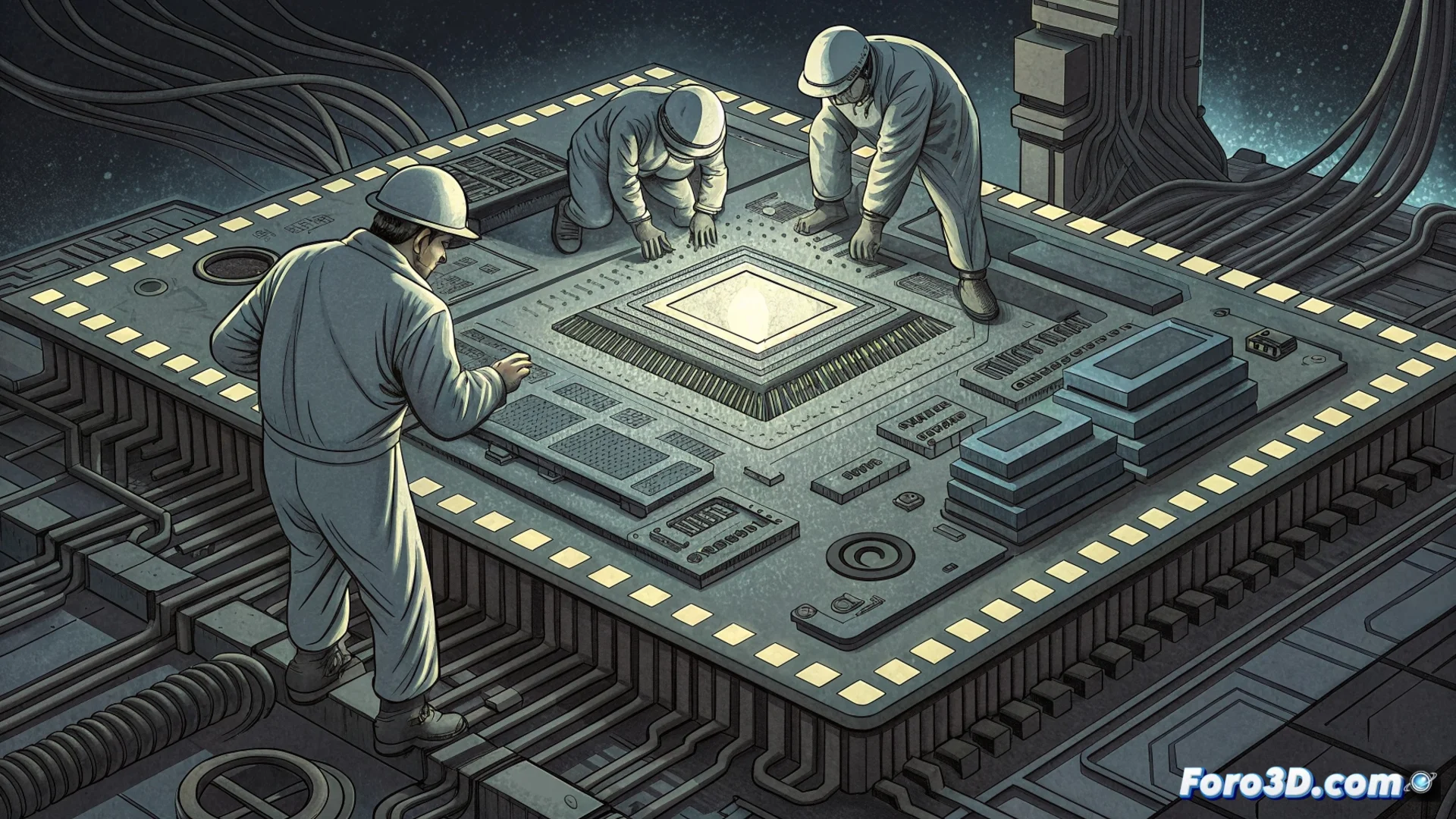

Intelは、AIアクセラレータの収益性の高い分野で地位を回復するための戦略を進めています。次の動きは、伝統的なモノリシック設計を放棄し、チップレットのモジュール式アーキテクチャを採用した巨大チップです。このシステムは、単一のパッケージに大量の計算リソースとメモリを統合し、モデル訓練の需要に直接対応します🤖。

多くの断片を統合することで生まれるパワー

このプロジェクトの鍵はチップレットアーキテクチャです。巨大な単一のシリコンチップを製造する代わりに、Intelは共通の基板に複数のタイルまたは専門化された断片を接続する計画です。この方法により、より効率的に性能をスケールアップでき、コストも抑えられます。これらのブロック間の相互接続が重要で、同社はデータがボトルネックなく流れるよう独自の高速度相互接続設計を使用します。

チップレットアプローチの主な利点:- 極端なサイズのモノリスの製造難を回避しつつ、より強力なチップを作成可能。

- シリコンウェハの歩留まりを向上させ、製造コストを削減。

- 同一パッケージ内で異なるタスク向けの専門化コアを使用しやすくする。

最大のチップを競うレースは、もはやシリコンの平方センチメートルではなく、どれだけの「タイル」を統合できるかで決まる。

大量の広帯域メモリ:AIの燃料

少なくとも16個の処理コアを駆動するために、Intelの設計には驚異的な量のメモリが含まれます。同一の封装内に次世代HBM5の24スタックを統合します。HBM(High Bandwidth Memory)は垂直に積層され、AIワークロードに不可欠な巨大な帯域幅を提供します。メモリを処理コアのすぐ隣に配置することで、レイテンシを最小化し、データフローを高速化します⚡。

この文脈でのHBM5メモリの特徴:- 多数のコアが継続的にデータを処理するための必要な帯域幅を提供。

- 第5世代は前世代より高い速度とエネルギー効率を約束。

- この先進的な統合は、現代のAIモデルが必要とする大量の情報を効率的に移動するのに理想的。

支配された市場での戦略的一手

この開発は単なる技術的試みではありません。Intelの戦略の中心的な柱であり、NVIDIAやAMDなどの確立されたプレーヤーと正面から競争するためのものです。AIモデル訓練に特化したこの強力なシステムにより、Intelは自身の技術的限界を超え、実現可能な代替案を提供できることを示そうとしています。最終目標は明確:高性能アクセラレータ市場の大きなシェアを獲得し、技術リーダーシップを回復することです🏆。