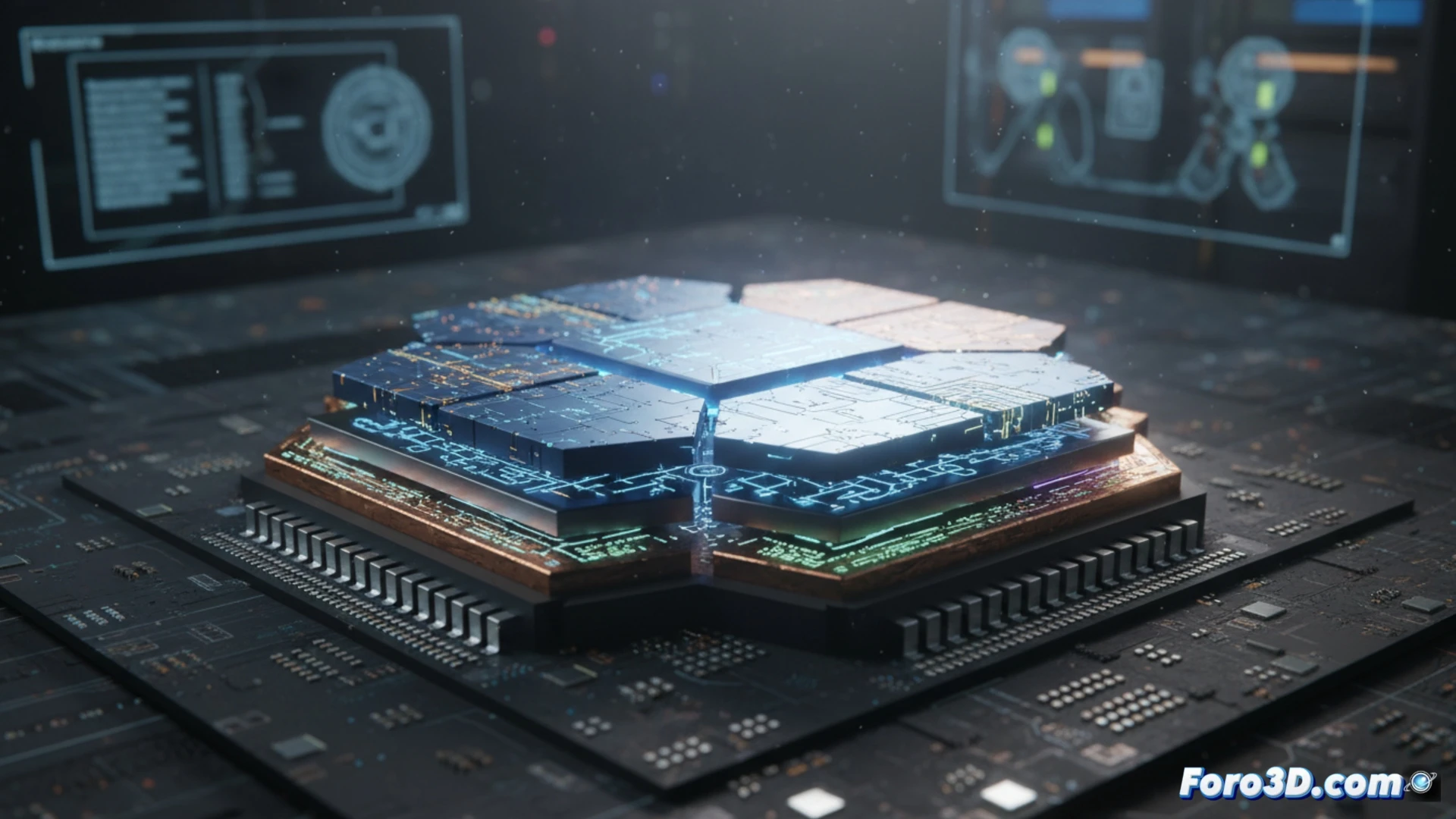

इंटेल कोर अल्ट्रा सीरीज 3, पैंथर लेक-एच का सूक्ष्मदर्शी विश्लेषण एक अप्रत्याशित ज्यामिति को उजागर करता है: एक अष्टकोणीय डाई। यह आकार इसकी चिपलेट वास्तुकला का भौतिक निशान है, जहां स्वतंत्र कार्यात्मक ब्लॉक्स अलग-अलग निर्मित होते हैं और एकत्रित किए जाते हैं। 3D मॉडलिंग समुदाय के लिए, यह डिज़ाइन एक आकर्षक अध्ययन का मामला है, क्योंकि इसकी आकृति और विभाजन सीधे प्रदर्शन, तापीय दक्षता और निर्माण लागत पर तकनीकी निर्णयों से जुड़े हैं।

3D विघटन: ब्लॉक्स, प्रक्रियाएं और मॉड्यूलर असेंबली 🔬

पैंथर लेक का एक सटीक 3D मॉडल उसके तीन मुख्य चिपलेट्स को दृश्य रूप से अलग करना चाहिए। केंद्रीय ब्लॉक SoC, जिसमें CPU और NPU शामिल हैं, Intel 18A में निर्मित एक अष्टकोण है। इससे जुड़ा ग्राफिक्स चिपलेट भिन्न होता है: H मॉडल्स में यह Intel 3 में 4 Xe कोर दिखाता है, जबकि कुशल U संस्करणों में इसे TSMC N3E में निर्मित 12 Xe कोर वाले चिपलेट से बदल दिया जाता है। अंत में, TSMC N6 में E/S ब्लॉक असेंबली को पूरा करता है। 3D विज़ुअलाइज़ेशन इस नोड्स की संकरता को समझने की अनुमति देता है जो प्रत्येक कार्य को अनुकूलित करता है: महत्वपूर्ण लॉजिक के लिए अग्रणी प्रक्रियाएं और E/S के लिए परिपक्व नोड्स, सब एक सामान्य सब्सट्रेट में परस्पर जुड़े हुए।

भविष्य मॉड्यूलर है: अर्धचालक डिज़ाइन 3D के लिए निहितार्थ 🧩

पैंथर लेक की अष्टकोणीय आकृति कोई शौक नहीं है, बल्कि विभिन्न आकारों और तकनीकों वाले आयताकार डाइज़ को एकीकृत करने के लिए पैकेजिंग का एक समाधान है जो उनके बीच की दूरी को न्यूनतम करता है। यह मॉड्यूलर दृष्टिकोण, परतों द्वारा 3D आरेखों से पूरी तरह चित्रण योग्य, भविष्य का मार्ग प्रशस्त करता है। अब एक एकल चिप का मॉडलिंग नहीं होता, बल्कि एक पैकेज में सिस्टम जहां प्रत्येक ब्लॉक की ज्यामिति, स्थानिक व्यवस्था और थर्मोडायनामिक्स 3D डिज़ाइनर के लिए महत्वपूर्ण चर हैं, जो एक उद्योग को प्रतिबिंबित करता है जो लचीलापन और विशेषीकृत अनुकूलन को प्राथमिकता देता है।

पैंथर लेक के चिपलेट की अष्टकोणीय ज्यामिति पारंपरिक आयताकार डिज़ाइनों की तुलना में तापीय प्रबंधन और 3D-हाइब्रिड एकीकरण पर कैसे प्रभाव डालती है?

(पीडी: 200mm वेफर का सिमुलेशन पिज़्ज़ा बनाने जैसा है: हर कोई एक टुकड़ा चाहता है)