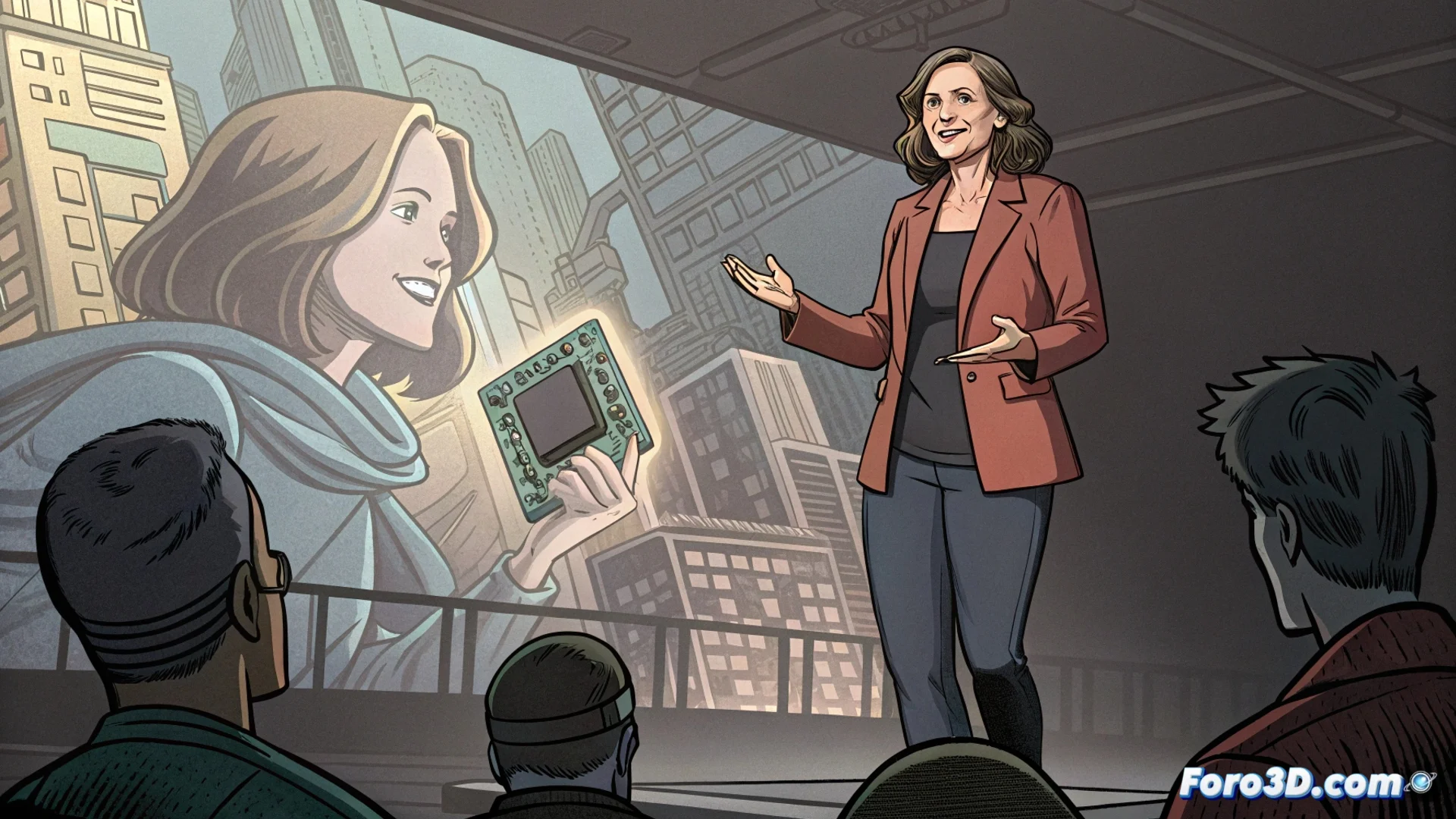

Lisa Su présente le processeur EPYC Venice avec Zen 6 au CES 2026

La scène du CES à Las Vegas a été le témoin d'une annonce clé pour le secteur des serveurs. Lisa Su, directrice exécutive d'AMD, a dévoilé deux produits stratégiques, mettant en lumière le nouveau processeur EPYC Venice qui implémente l'architecture Zen 6. La révélation la plus impactante a été son design physique radical, qui marque un point d'inflexion dans la manière dont ces composants sont construits. 🚀

Un design qui rompt avec la convention thermique

Le processeur Venice a été présenté sans sa tapa de distribution thermique (IHS), un élément standard dans l'industrie. Cette décision d'exposer les chiplets n'est pas un simple geste visuel, mais un choix technique profond. En éliminant cette couche intermédiaire, AMD vise à permettre au système de refroidissement de faire contact direct avec les sources de chaleur primaires.

Avantages clés du design ouvert :- Réduire la résistance thermique : Éliminer l'interface entre le silicium et le dissipateur permet que la chaleur se transfère de manière plus efficace.

- Activer un emballage sophistiqué : Cette approche est fondamentale pour utiliser des techniques d'assemblage plus avancées, que AMD n'a pas détaillées complètement.

- Optimiser pour des charges soutenues : Le bénéfice direct est que le processeur peut maintenir des fréquences d'horloge élevées plus longtemps ou consommer moins d'énergie pour exécuter les mêmes tâches.

Dans le monde des serveurs, montrer l'intérieur n'est plus de la mauvaise éducation, mais une déclaration d'intentions techniques.

L'architecture Zen 6 et son contexte compétitif

Ce lancement ne se comprend pas sans la base que fournit Zen 6. La combinaison de cette nouvelle microarchitecture avec la méthode révolutionnaire d'emballage est clairement destinée à dominer le marché des centres de données et de la computación en la nube, segments où l'efficacité et le rendement par watt sont critiques.

Objectifs stratégiques du projet Venice :- Concourir en haute performance : Se positionner face à d'autres solutions pour serveurs avec une proposition technique différenciée.

- Améliorer la gestion de l'énergie : Le design thermique supérieur est intrinsèquement lié à une meilleure administration de la puissance dans des environnements à haute densité.

- Adopter l'innovation en packaging : La présentation souligne que cette étape est nécessaire pour implémenter la prochaine génération de technologie d'emballage, cruciale pour l'évolution des puces.

Une déclaration de principes pour l'industrie

La présentation de Lisa Su au CES 2026 transcende le lancement d'un produit. Le processeur EPYC Venice symbolise un changement de philosophie : prioriser l'efficacité technique extrême sur les conventions de design. En exposant le cœur de silicium, AMD ne montre pas seulement une puce, mais défie l'industrie à repenser comment construire du matériel pour les défis computationnels du futur. Le message est clair : dans la quête de performance, chaque couche éliminée compte. 💡