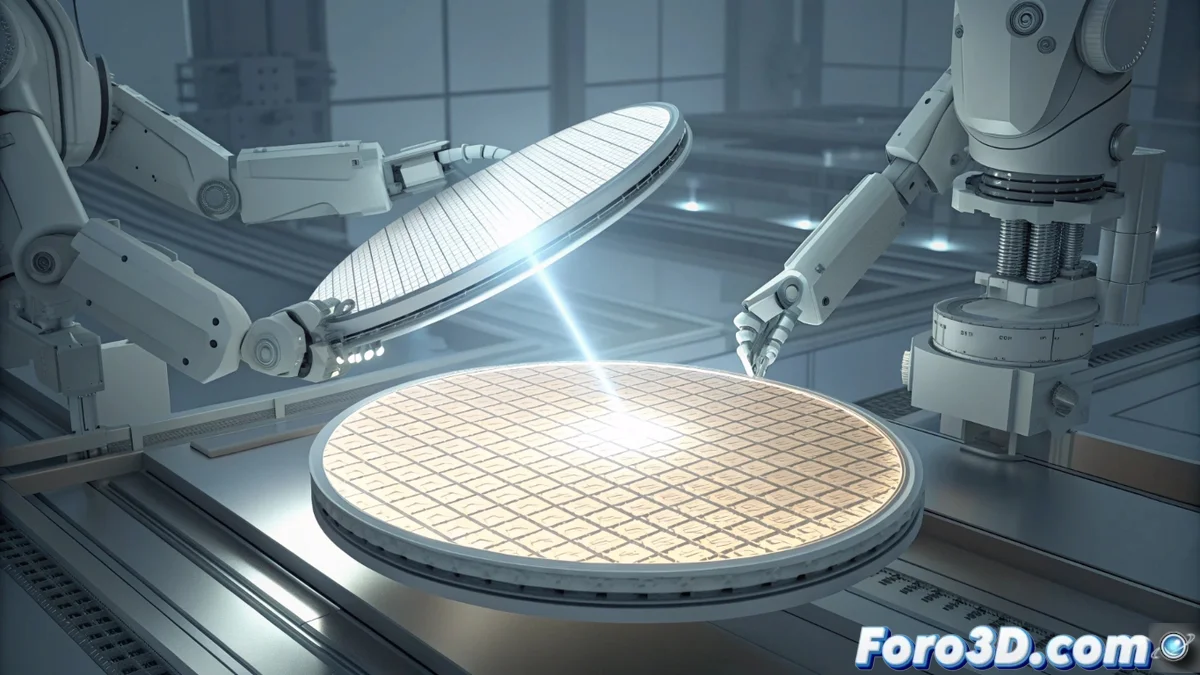

Wafer-on-wafer bonding : la technique d'empaquetage 3D extrême

Dans la quête de plus de puissance et d'efficacité, l'industrie des semi-conducteurs avance vers la troisième dimension. L'une des méthodologies les plus radicales est le Wafer-on-Wafer (WoW) bonding, qui fusionne deux obleas de silicium complètes avant de les séparer en puces individuelles. Cette méthode contraste avec les approches traditionnelles et permet une intégration de systèmes sans précédent. 🚀

Le processus d'union nanométrique

La technique n'empile pas des puces déjà découpées, mais opère à un niveau antérieur. D'abord, deux obleas sont traitées de manière indépendante, chacune avec ses propres transistors et circuits. Ensuite, un équipement d'alignement de haute précision les place face à face avec une exactitude nanométrique. L'union permanente est obtenue en appliquant de la chaleur et une pression contrôlées, créant un bloc monolithique de silicium. À l'intérieur de ce bloc, les canaux électriques entre les deux moitiés sont incroyablement denses et courts. Ce n'est qu'après cette fusion que le bloc est découpé pour obtenir les dispositifs 3D finaux.

Avantages clés du WoW bonding :- Densité d'interconnexion extrême : Se connecter au niveau de l'oblea permet des milliers de fois plus de voies de communication que avec des microbumps.

- Chemin de signal ultra court : Les données parcourent des distances minimales entre les modules, ce qui accélère le transfert et réduit la consommation d'énergie.

- Intégration de système complet : Facilite l'union, par exemple, d'unités de traitement logique et de banques de mémoire à haute vitesse dans un seul dispositif compact.

Le vrai défi n'est pas d'unir les obleas, mais d'éviter qu'elles se collent de manière accidentelle pendant la fabrication, un problème que tout ingénieur connaît trop bien.

Comparaison avec d'autres techniques 3D

Des méthodes comme le empilement de puces (Chip-on-Chip) ou l'utilisation de Through-Silicon Vias (TSVs) ont des limitations inhérentes. Dans ces cas, les connexions verticales (microbumps ou TSVs) sont physiquement plus grandes et plus espacées, créant un goulot d'étranglement pour la communication. Le WoW bonding élimine cet obstacle en interconnectant les transistors d'une oblea directement avec ceux de l'autre à l'échelle microscopique. Cela transforme la façon dont l'information circule entre les différents blocs fonctionnels d'un système.

Différences principales :- Échelle de connexion : WoW opère au niveau transistor/oblea, tandis que les autres techniques le font au niveau puce/empaquetage.

- Espacement entre voies : La densité d'interconnexions en WoW est d'ordres de grandeur supérieure.

- Processus de fabrication : WoW unit avant de découper, ce qui simplifie la manipulation et l'alignement de composants extrêmement petits.

Défis et avenir de l'intégration 3D

Mettre en œuvre cette technologie n'est pas exempt d'obstacles. En plus du risque d'adhésion prématurée des obleas, des salles blanches avec des niveaux de propreté exceptionnels et des équipements d'alignement très coûteux sont nécessaires. Cependant, la récompense justifie l'effort : des systèmes complets, plus rapides et efficaces, emballés dans un espace minimum. Cette évolution est cruciale pour suivre la Loi de Moore et alimenter la prochaine génération d'informatique, d'intelligence artificielle et de dispositifs mobiles. Le WoW bonding représente un saut conceptuel dans la façon dont nous construisons l'électronique. 💡