Intel conçoit un chiplet énorme avec HBM5 pour concurrencer en IA

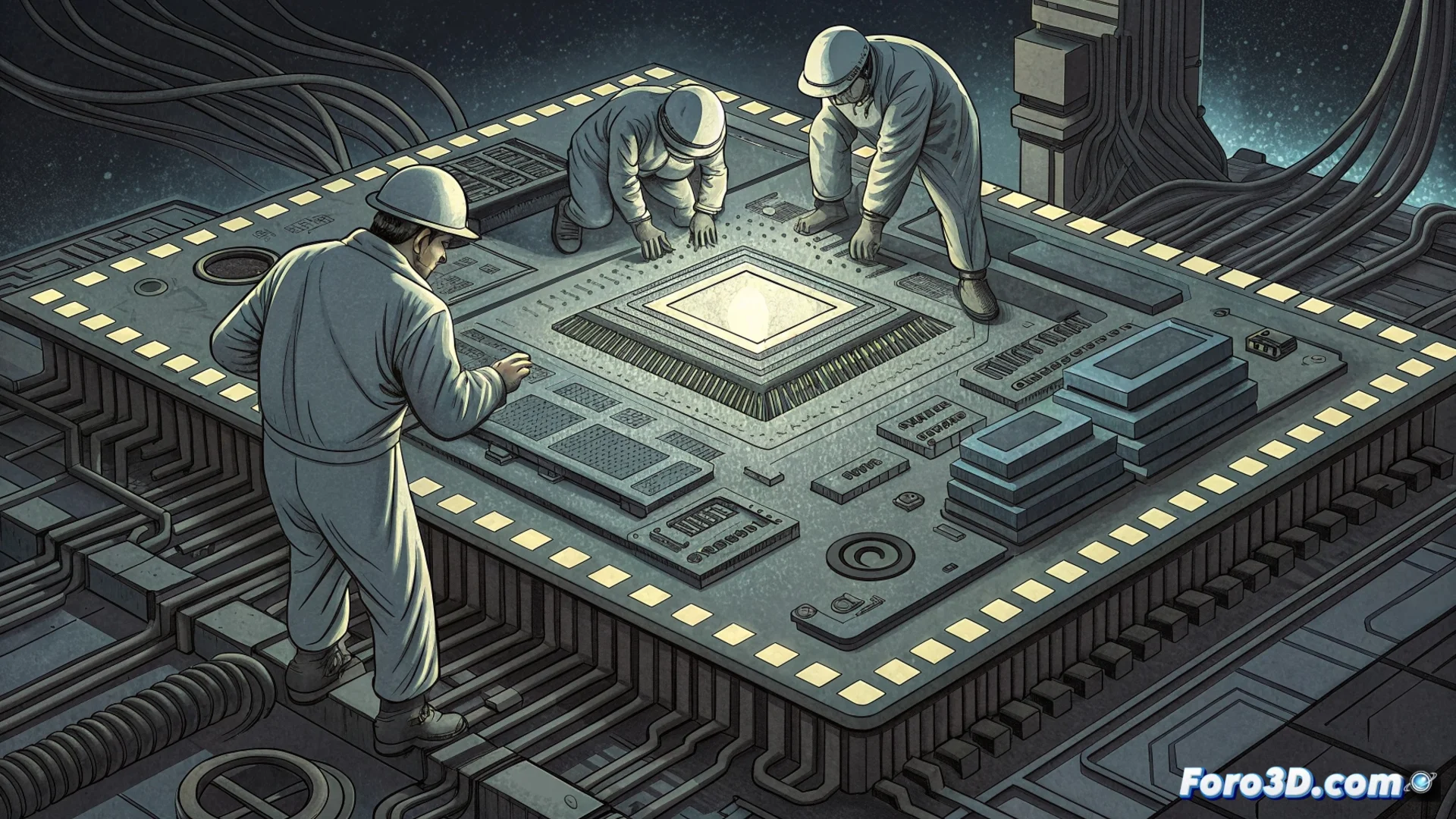

Intel avance dans sa stratégie pour regagner du terrain dans le lucratif domaine des accélérateurs d'IA. Son prochain mouvement est un chip colossal qui abandonne le design monolithique traditionnel pour adopter une architecture modulaire de chiplets. Ce système intégrera une quantité massive de ressources de calcul et de mémoire dans un seul package, visant directement les exigences de l'entraînement de modèles 🤖.

La puissance naît de l'union de nombreux fragments

La clé de ce projet est l'architecture chiplet. Au lieu de fabriquer un seul morceau de silicium géant, Intel prévoit de connecter de multiples tiles ou fragments spécialisés sur un substrat commun. Cette méthode permet d'échelonner les performances de manière plus efficace et à moindre coût. L'interconnexion entre ces blocs est fondamentale, et l'entreprise utilise son propre design d'interconnexion à haute vitesse pour que les données circulent sans goulots d'étranglement.

Avantages clés de l'approche chiplet :- Permet de créer un chip plus puissant sans les difficultés de produire un monolithe de taille extrême.

- Réduit les coûts de fabrication en améliorant le rendement des plaquettes de silicium.

- Facilite l'utilisation de cœurs spécialisés pour des tâches différentes au sein du même package.

La course au chip le plus grand ne se mesure plus en centimètres carrés de silicium, mais en combien de 'tiles' tu peux intégrer.

Mémoire à large bande passante massive : le carburant pour l'IA

Pour alimenter ses au moins seize cœurs de traitement, le design d'Intel inclut une quantité extraordinaire de mémoire. Il intégrera vingt-quatre piles de la prochaine génération HBM5 au sein du même encapsulé. La mémoire HBM (High Bandwidth Memory) est empilée verticalement, offrant une bande passante énorme qui est critique pour les charges de travail d'IA. En plaçant la mémoire juste à côté des cœurs processeurs, on minimise la latence et on accélère le flux de données ⚡.

Caractéristiques de la mémoire HBM5 dans ce contexte :- Fournit la bande passante nécessaire pour que les nombreux cœurs processeurs traitent les données de manière continue.

- La cinquième génération promeut une plus grande vitesse et une efficacité énergétique que ses prédécesseurs.

- Cette intégration avancée est idéale pour déplacer les quantités massives d'informations requises par les modèles d'IA modernes.

Un coup stratégique sur un marché dominé

Ce développement n'est pas seulement un exercice technique. Il représente un pilier central dans la stratégie d'Intel pour concurrencer de front des acteurs établis comme Nvidia et AMD. En créant un système aussi puissant et spécifique pour entraîner des modèles d'IA, Intel cherche à démontrer qu'il peut dépasser ses propres limites techniques et offrir une alternative viable. L'objectif final est clair : capturer une part significative du marché des accélérateurs haute performance et retrouver le leadership technologique 🏆.