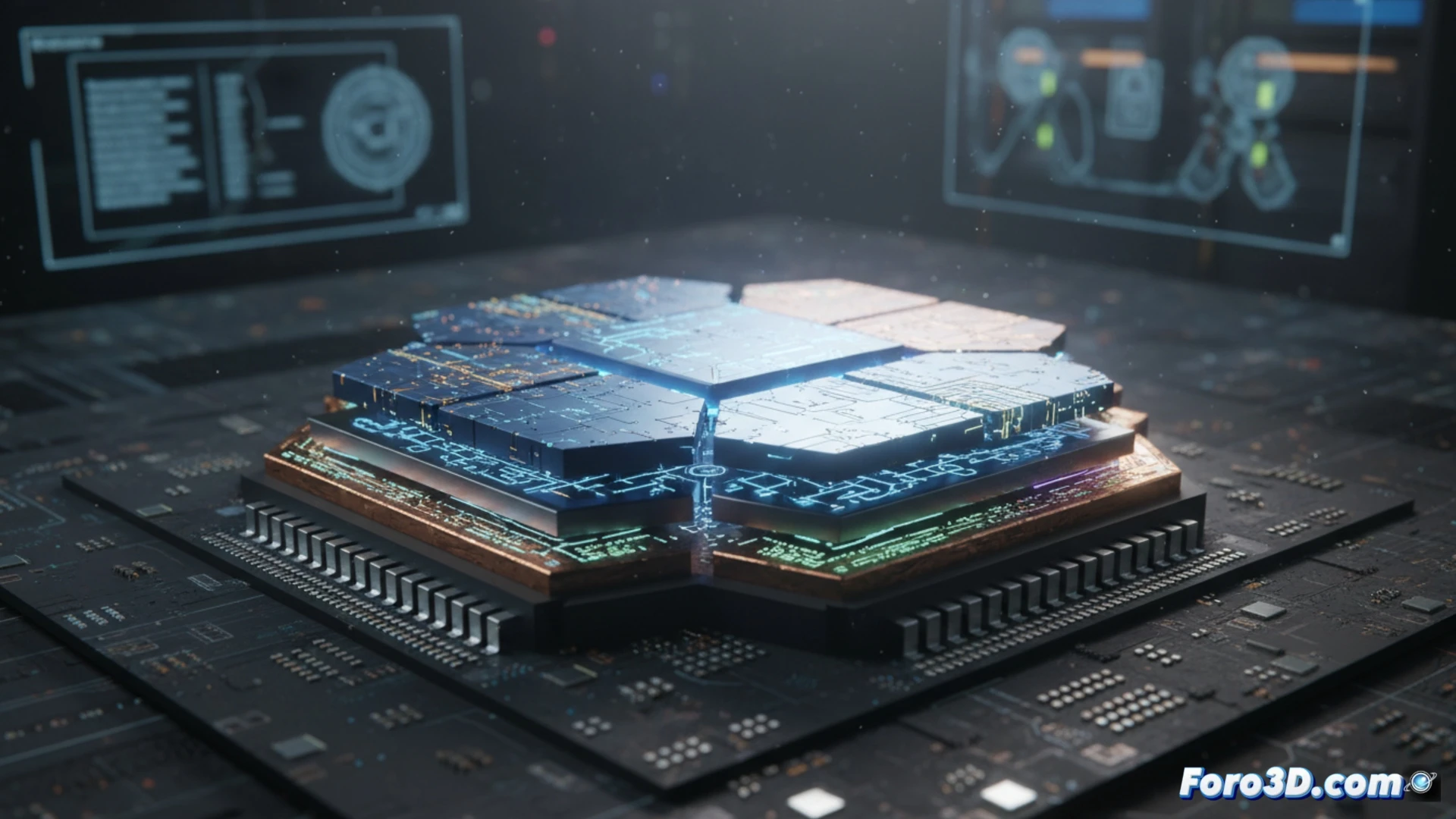

Microscopic analysis of the Intel Core Ultra Series 3, Panther Lake-H, has revealed an unexpected geometry: an octagonal die. This shape is the physical footprint of its chiplet architecture, where independent functional blocks are manufactured separately and assembled. For the 3D modeling community, this design is a fascinating case study, as its shape and partitioning directly respond to technical decisions on performance, thermal efficiency, and manufacturing cost.

3D Deconstruction: Blocks, Processes, and Modular Assembly 🔬

An accurate 3D model of Panther Lake must visually separate its three key chiplets. The central SoC block, with CPU and NPU, is an octagon manufactured on the advanced Intel 18A. Attached to it, the graphics chiplet varies: in H models it features 4 Xe cores on Intel 3, while in efficient U versions it is replaced by a chiplet with 12 Xe cores manufactured on TSMC N3E. Finally, the I/O block, on TSMC N6, completes the assembly. 3D visualization allows understanding how this node hybridization optimizes each function: cutting-edge processes for critical logic and mature nodes for I/O, all interconnected on a common substrate.

The Future is Modular: Implications for 3D Semiconductor Design 🧩

The octagonal shape of Panther Lake is not a whim, but a packaging solution to integrate rectangular dies of different sizes and technologies while minimizing the distance between them. This modular approach, perfectly illustratable through layered 3D diagrams, marks the future path. Chips are no longer modeled as monolithic, but as a system in a package where the geometry, spatial arrangement, and thermodynamics of each block are critical variables for the 3D designer, reflecting an industry that prioritizes flexibility and specialized optimization.

How does the octagonal geometry of the Panther Lake chiplet influence thermal management and 3D-hybrid integration compared to traditional rectangular designs?

(PS: simulating a 200mm wafer is like making a pizza: everyone wants a slice)