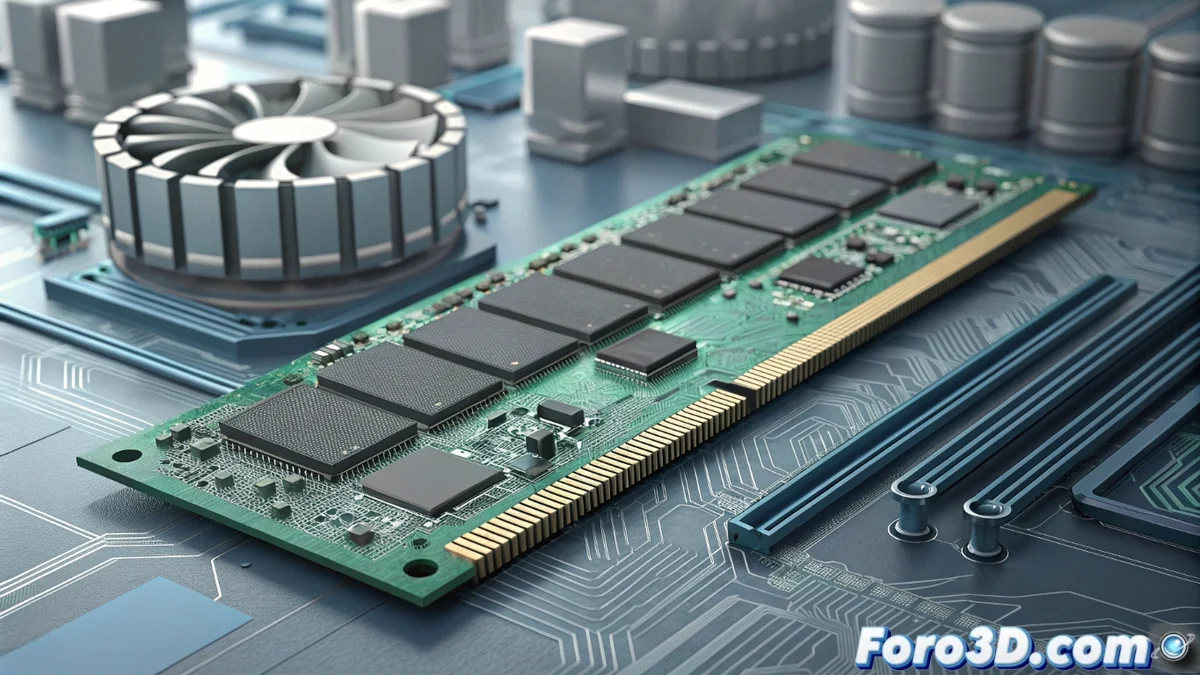

DDR5 MCR DIMM Memory Doubles Bandwidth in Servers

The evolution in server architecture demands more efficient memory solutions. MCR DIMM (Multiplexer Combined Ranks) represent a significant advancement, integrating a multiplexer buffer directly into the module. This component allows doubling the effective bandwidth, a critical need for modern processors in AI and intensive computing environments. 🚀

The Core of the Innovation: The Multiplexer Buffer

The operation of this technology is based on a special integrated circuit that acts as an intermediary. Instead of the CPU's memory controller accessing chips sequentially, the buffer manages two ranks of DDR5 memory independently and simultaneously. It combines data streams before sending them to the processor, saturating the memory bus with more information per clock cycle. It does not accelerate the base frequency, but makes the most of the available bandwidth.

Key Features of the MCR Buffer:- Acts as a multiplexer that combines two data channels into one.

- Allows reading and writing to two DDR5 chip ranks at the same time.

- Presents a unified data stream of greater bandwidth to the CPU.

The idea of doubling the bandwidth sounds good until you remember that now the bottleneck will have happily moved to another part of the system. There's always a slower link in the chain.

Transforming Performance in Data Centers

For large-scale infrastructures, MCR DIMM offer a strategic advantage. They allow scaling the total memory bandwidth without increasing the number of physical slots on the motherboard or CPU channels. This optimizes compute density per rack and improves energy efficiency, decisive factors in data center operations.

Benefits for Specific Workloads:- Training AI Models: Feeds GPUs and TPUs with large volumes of data consistently.

- Running in-memory databases: Accelerates access and processes transactions.

- Performing scientific analysis and simulation: Reduces data wait times.

A Step Toward More Balanced Systems

The adoption of DDR5 MCR DIMM mitigates one of the main bottlenecks in high-performance servers. By providing more data per cycle, it allows powerful processing units to maintain a sustained work pace. However, as the quote points out, a system's total performance will always be limited by its slowest component, so this technology must be integrated into a balanced architecture. The future of intensive computing depends on innovations like this that optimize every link in the chain. ⚙️