Lyra: a Generative Framework for Verifying RISC-V Processors

Verifying complex RISC-V processor designs is a major challenge. Traditional methods, which rely on slow software simulation and random test stimuli, represent a significant bottleneck. Lyra emerges as an innovative solution that addresses this problem at its root, integrating artificial intelligence directly into the workflow. 🚀

An Intelligent Approach to Generating Tests

Instead of relying on blind mutations or random vectors, Lyra incorporates a specialized generative model called LyraGen. This model deeply understands the processor's instruction set architecture (ISA). Its main function is to produce semantically rich, high-quality instruction sequences, specifically designed to explore complex behaviors and hardware design corners that random methods overlook.

Key Advantages of LyraGen:- Generates test stimuli that understand RISC-V instruction semantics.

- Targetedly explores complex internal hardware states.

- Replaces simple randomness with meaningful instruction sequences.

What chip design needs is for an AI to explain which instructions are interesting to execute, not randomly hitting the keyboard until something fails.

Massive Acceleration through Hardware Execution

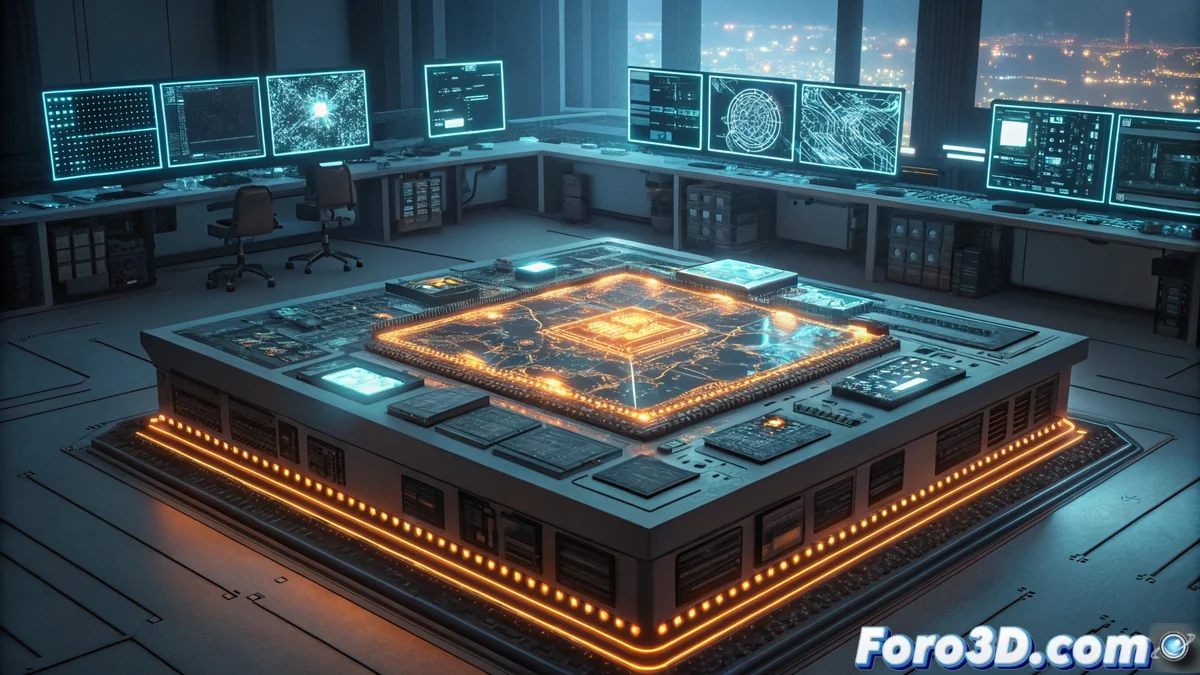

Lyra's architecture is not only intelligent in test generation but also extremely fast in execution. The system implements the unit under test and a golden reference model in parallel within an FPGA-based SoC. This approach enables comparing differences between both at hardware speed, achieving monumental acceleration. Additionally, it facilitates collecting coverage metrics massively and in real-time, something prohibitive with software simulators.

Results of Accelerated Verification:- Executes comparison and verification at the FPGA's native speed.

- Collects coverage data comprehensively and efficiently.

- Combines LyraGen's intelligent generation with hardware speed.

Empirical Results Demonstrating Its Superiority

Experimental tests with Lyra show quantifiable and substantial improvements over the most advanced traditional software verifiers. The system achieves design coverage up to 1.27 times higher, finding more edge cases and critical states. In terms of speed, it accelerates the complete end-to-end verification process between 107 and 3343 times. Another key benefit is consistently lower convergence difficulty, which directly translates to reducing the total cost and time needed to verify a complex design. ✅