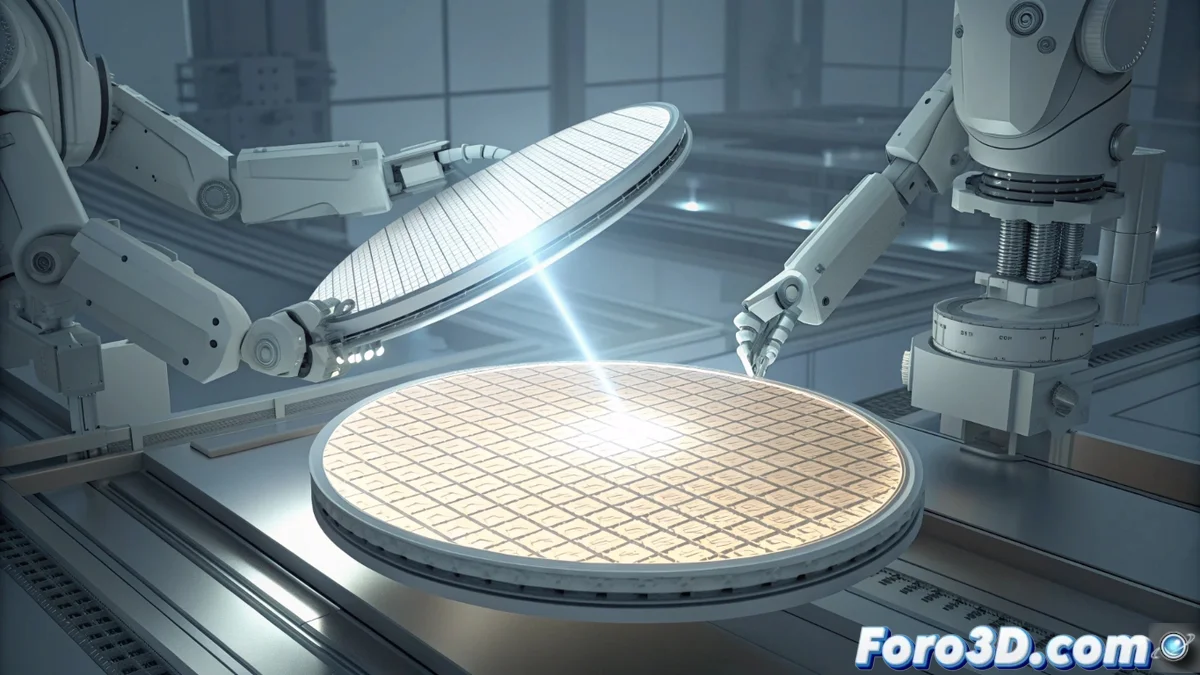

Wafer-on-Wafer-Bonding: die Technik für extremes 3D-Paketieren

Im Streben nach mehr Leistung und Effizienz rückt die Halbleiterindustrie in die dritte Dimension vor. Eine der radikalsten Methoden ist das Wafer-on-Wafer (WoW) Bonding, das zwei vollständige Siliziumwafer fusioniert, bevor sie in einzelne Chips getrennt werden. Diese Methode unterscheidet sich von traditionellen Ansätzen und ermöglicht eine beispiellose Systemintegration. 🚀

Der Prozess der nanometrischen Verbindung

Die Technik stapelt keine bereits geschnittenen Chips, sondern arbeitet auf einer früheren Ebene. Zuerst werden zwei Wafer unabhängig voneinander verarbeitet, jeder mit seinen eigenen Transistoren und Schaltkreisen. Dann platziert ein hochpräzises Ausrichtungssystem sie gesicht zu gesicht mit nanometrischer Genauigkeit. Die permanente Verbindung wird durch kontrollierte Hitze und Druck erreicht, wodurch ein monolithischer Siliziumblock entsteht. Innerhalb dieses Blocks sind die elektrischen Kanäle zwischen den beiden Hälften unglaublich dicht und kurz. Erst nach dieser Fusion wird der Block geschnitten, um die finalen 3D-Geräte zu erhalten.

Schlüssige Vorteile des WoW-Bondings:- Extreme Interkonnektionsdichte: Die Verbindung auf Wafer-Ebene ermöglicht Tausende Male mehr Kommunikationswege als Microbumps.

- Ultrakurzer Signalweg: Die Daten legen minimale Distanzen zwischen Modulen zurück, was die Übertragung beschleunigt und den Energieverbrauch reduziert.

- Vollständige Systemintegration: Ermöglicht z. B. die Verbindung von Logikprozessoren und Hochgeschwindigkeits-Speicherbänken in einem kompakten Gerät.

Die wahre Herausforderung ist nicht, die Wafer zu verbinden, sondern zu verhindern, dass sie während der Fertigung versehentlich haften bleiben – ein Problem, das jeder Ingenieur zu gut kennt.

Vergleich mit anderen 3D-Techniken

Methoden wie das Chip-Stapeln (Chip-on-Chip) oder die Verwendung von Through-Silicon Vias (TSVs) haben inhärente Einschränkungen. In diesen Fällen sind die vertikalen Verbindungen (Microbumps oder TSVs) physisch größer und weiter auseinander, was einen Engpass für die Kommunikation schafft. Das WoW-Bonding eliminiert dieses Hindernis, indem es die Transistoren eines Wafers direkt mit denen des anderen auf mikroskopischer Skala verbindet. Dies verändert, wie Informationen zwischen den verschiedenen funktionalen Blöcken eines Systems fließen.

Hauptunterschiede:- Verbindungsmaßstab: WoW arbeitet auf Transistor/Wafer-Ebene, während andere Techniken auf Chip/Paket-Ebene operieren.

- Abstand zwischen den Vias: Die Interkonnektionsdichte bei WoW ist um Größenordnungen höher.

- Fertigungprozess: WoW verbindet vor dem Schneiden, was den Umgang und die Ausrichtung extrem kleiner Komponenten vereinfacht.

Herausforderungen und Zukunft der 3D-Integration

Die Implementierung dieser Technologie ist nicht ohne Hindernisse. Neben dem Risiko einer vorzeitigen Haftung der Wafer werden Reinräume mit außergewöhnlichen Reinheitsgraden und hochpreisige Ausrichtungssysteme benötigt. Dennoch rechtfertigt die Belohnung den Aufwand: vollständige Systeme, die schneller und effizienter sind und in minimalem Raum gepackt werden. Diese Entwicklung ist entscheidend, um der Mooreschen Gesetz zu folgen und die nächste Generation von Rechenzentren, Künstlicher Intelligenz und mobilen Geräten zu versorgen. Das WoW-Bonding stellt einen konzeptionellen Sprung dar, wie wir Elektronik bauen. 💡