Intel präsentiert seine Glas-Substrat-Technologie auf der Nepcon Japan 2026

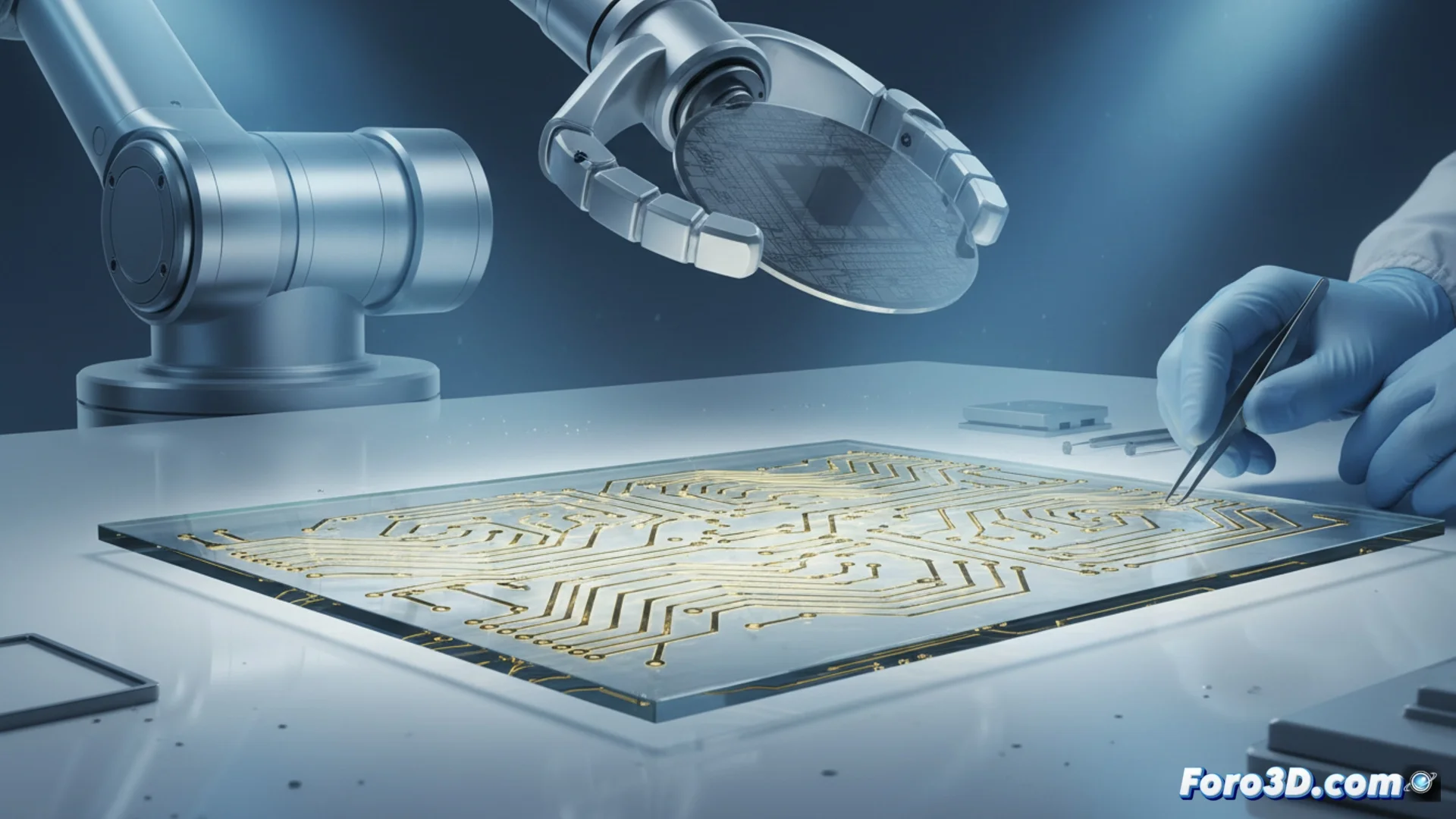

Das Unternehmen Intel hat seine neue Glas-Substrate auf der Veranstaltung Nepcon Japan 2026 vorgestellt. Diese Entwicklung entsteht, um der wachsenden Nachfrage nach der Herstellung von integrierten Schaltkreisen mit höherer Dichte und Leistung gerecht zu werden, insbesondere für KI-Beschleuniger und das Feld der Supercomputing. Die Technologie ermöglicht es, mehr Elemente in einer einzigen Einheit zu verpacken, was Prozessoren hilft, komplexe Aufgaben effizienter zu bewältigen. 🚀

Schlüsseltechnische Vorteile der Glas-Substrate

Diese innovative Lösung verwendet Glas als Basis material, das traditionelle organische oder keramische Substrate ersetzt. Glas weist überlegene physikalische Eigenschaften auf, wie eine verbesserte dimensionsstabile und eine außergewöhnliche Planheit. Dies ermöglicht es Herstellern, Verbindungsbahnen dünner zu gestalten und Transistoren in größerer Nähe zueinander zu platzieren.

Hauptvorteile dieser Technologie:- Es wird eine größere Bandbreite für die Datenübertragung erreicht.

- Die Latenz in der Kommunikation zwischen den verschiedenen Chip-Kernen wird reduziert.

- Es wird erleichtert, die Leistung zu steigern, ohne die physische Größe oder den Energieverbrauch übermäßig zu erhöhen.

Die Glas-Substrat-Technologie markiert einen Wendepunkt für die Verpackung von Chips mit höchster Leistung und ermöglicht zuvor unmögliche Dichten.

Fokus auf Künstliche Intelligenz und Supercomputing

Intel richtet diese Neuheit hauptsächlich auf den Bereich der KI-Beschleuniger und Supercomputer aus. Schaltkreise, die diese Substrate verwenden, können eine größere Anzahl von Verarbeitungskernen und schnellem Speicher in einem kompakten Raum beherbergen.

Kritische Anwendungen, die ermöglicht werden:- Ausbildung von KI-Modellen großen Umfangs und Komplexität.

- Simulation von wissenschaftlichen Phänomenen, die eine enorme Rechenleistung erfordern.

- Skalierung der Rechenleistung bei kontrolliertem Energieverbrauch.

Zukunftsprognosen und Überlegungen

Dieser technische Fortschritt legt den Grundstein für die nächste Generation von High-Performance-Prozessoren. Die Fähigkeit, mehr Komponenten effizient zu integrieren, ist entscheidend, um mit der Nachfrage nach Leistung in KI und HPC Schritt zu halten. Die anhaltende Herausforderung wird sein, dass die Herstellungskosten dieser futuristischen Chips den Endpreis für den Nutzer nicht übermäßig belasten. 💡